# CD08AD1500

8 位、双路 1.5GSPS 或单路 3.0GSPS 模数转换器 (ADC)

版本: Rev 1.0.0 日期: 2025-5-20

## 产品特性

- 双通道超高速 A/D 转换器

- 8 位分辨率

- 单电源 $+1.9V \pm 0.1V$  工作

- SDR 或 DDR 输出时钟选择

- 每通道采样率 1.5GSPS, 采用时间交替模式可达到 2 倍采样率

- 多路 ADC 同步性能

- 时钟占空比校正

- 最大转换速率: 1.5GSPS

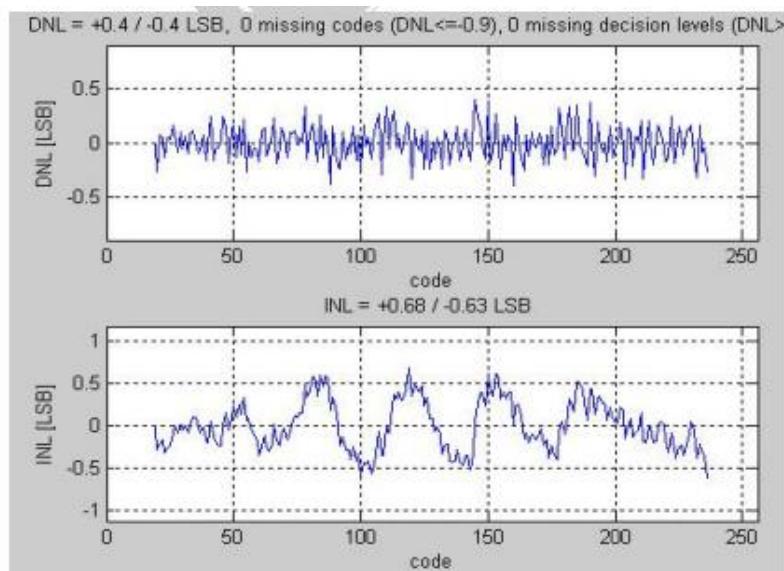

- DNL:  $\pm 0.4LSB$

- 扩展控制为串行接口:

- 4 位地址, 16 位数据

- 输入满刻度范围数字调节

## 产品应用

- 数字示波器

- 通信接收机

- 直接 RF 下变频转换器

- 高速数字采集

- 雷达、电子对抗

- 数字示波器

## 产品描述

CD08AD1500 是采用 CMOS 工艺制造的半导体集成电路。该产品为折叠和插值相结合的结构，电路内部包含采样/保持放大器、折叠放大器、带隙电压基准、时钟电路和 LVDS 输出等电路。

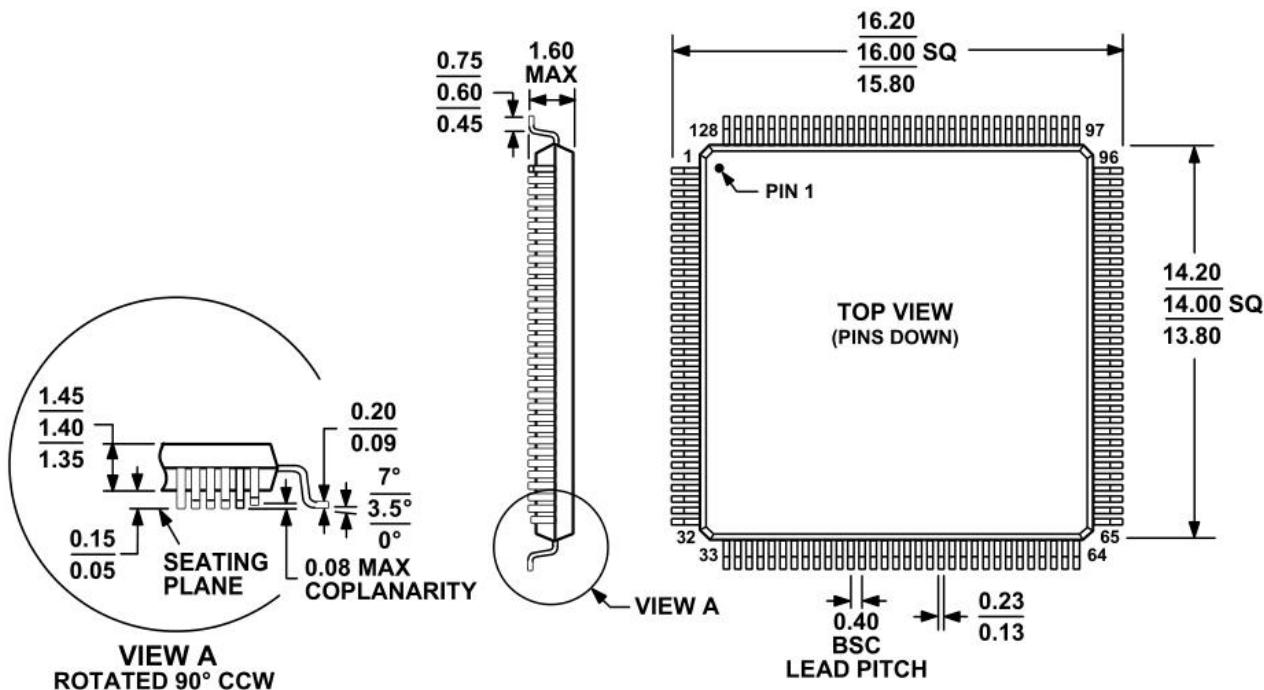

该电路采用 128 引线四面扁平外壳封装 (TQFP128)，外形尺寸为  $22mm \times 22mm \times 2mm$ ，执行标准 GJB597A-1996。该产品具有采样率高、功耗低、线性误差小、增益和失调自动校正和 3 - 线接口控制等特点。通过 3 - 线接口可对内部电路的增益、失调和通道间的时钟匹配进行校正，模拟输入为差分输入，即可交流耦合也可直流耦合；时钟输入电路内部设有直流偏置，必须交流耦合输入。

该产品与国外 National Semiconductor 公司产品 ADC08D1500 管脚排列相同，功能和性能可直接替换 ADC08D1500。

## 目录

|                |        |

|----------------|--------|

| 产品特性 .....     | - 1 -  |

| 产品应用 .....     | - 1 -  |

| 产品描述 .....     | - 1 -  |

| 功能框图 .....     | - 3 -  |

| 引脚配置 .....     | - 4 -  |

| 时序图 .....      | - 7 -  |

| 输出码 .....      | - 10 - |

| 推荐工作条件 .....   | - 10 - |

| 推绝对最大额定值 ..... | - 11 - |

| 性能参数 .....     | - 11 - |

| 应用说明 .....     | - 14 - |

| 注意事项 .....     | - 22 - |

| 产品外形图 .....    | - 23 - |

| 包装/订购信息 .....  | - 23 - |

| 修订日志 .....     | - 24 - |

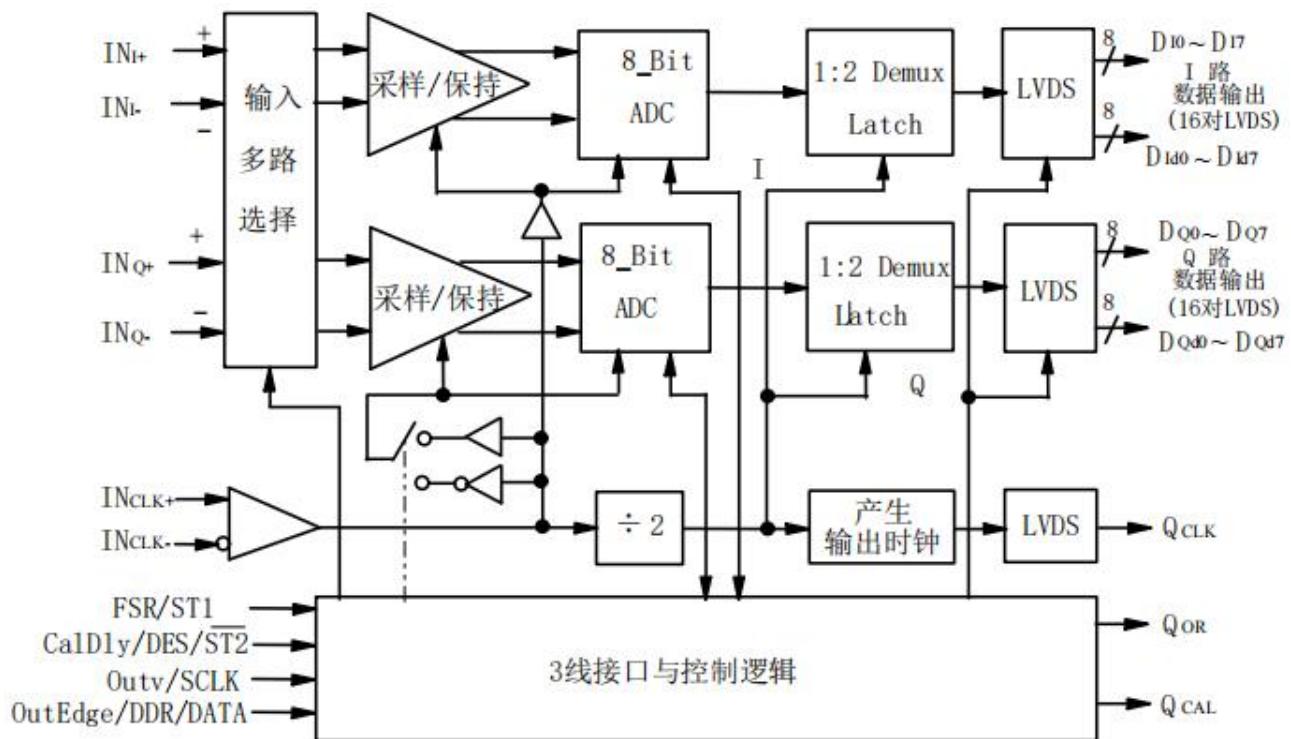

## 功能框图

18 位 5MSpsA/D 转换器功能框图如图 1。

图 1. 功能框图

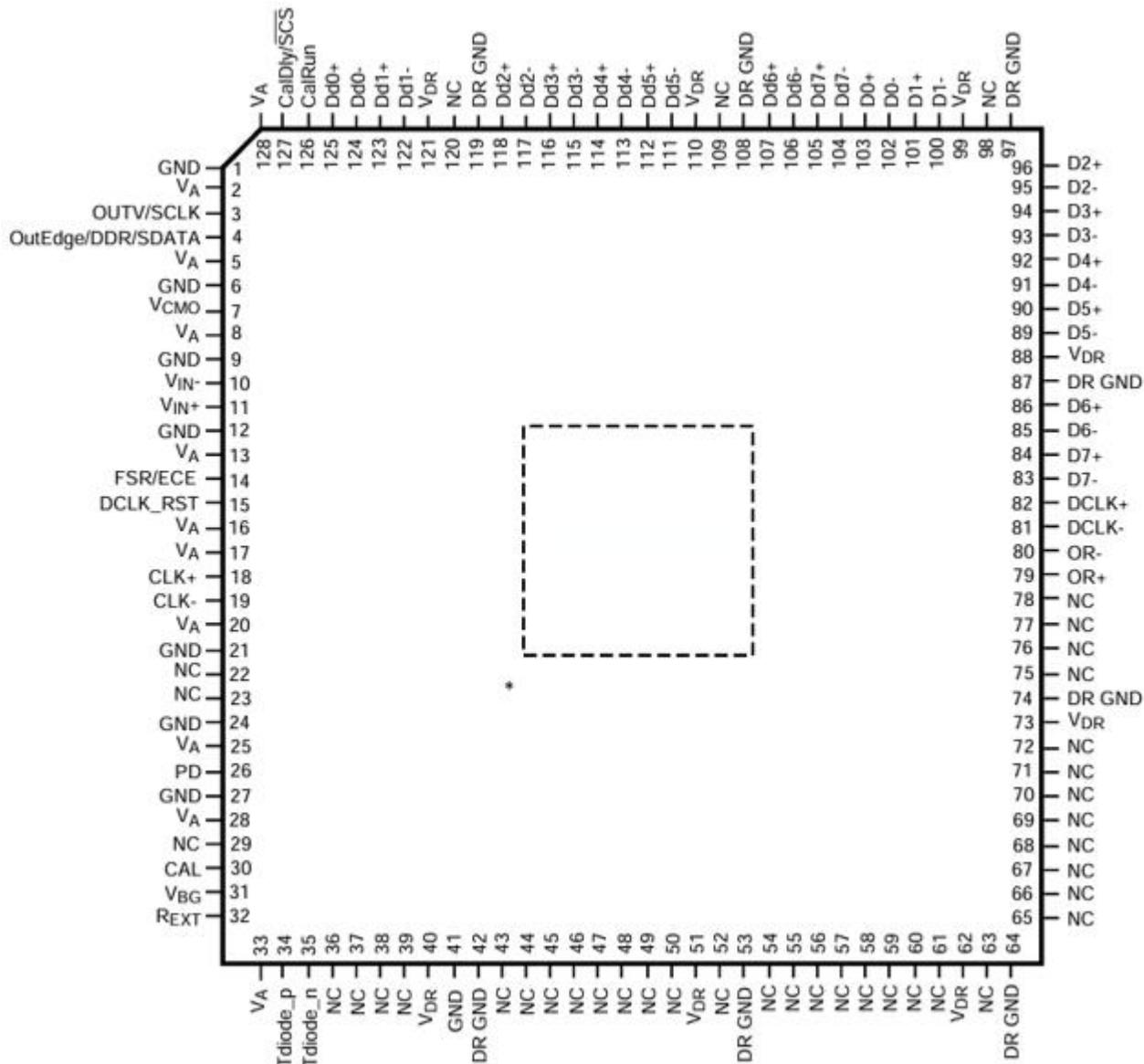

## 引脚配置

引脚配置

| 引脚编号 | 符号                   | 功能                     | 引脚编号 | 符号              | 功能                       |

|------|----------------------|------------------------|------|-----------------|--------------------------|

| 1    | GND <sub>D</sub>     | 模拟地                    | 65   | D <sub>Q2</sub> | Q 路数据输出位 D <sub>Q2</sub> |

| 2    | V <sub>CC</sub>      | 模拟电源                   | 66   | D <sub>Q2</sub> | Q 路数据输出位 D <sub>Q2</sub> |

| 3    | Outv/SCLK            | 输出电压幅度控制/串行接口时钟输入      | 67   | D <sub>Q3</sub> | Q 路数据输出位 D <sub>Q3</sub> |

| 4    | OutEdge/<br>DDR/DATA | 输出时钟沿选择/双数据速率控制/串行数据输入 | 68   | D <sub>Q3</sub> | Q 路数据输出位 D <sub>Q3</sub> |

|    |                     |                     |    |                  |                                   |

|----|---------------------|---------------------|----|------------------|-----------------------------------|

| 5  | V <sub>CC</sub>     | 模拟电源                | 69 | D <sub>Q4</sub>  | Q 路数据输出位 D <sub>Q4</sub>          |

| 6  | GND <sub>A</sub>    | 模拟地                 | 70 | D <sub>Q4</sub>  | Q 路数据输出位 D <sub>Q4</sub>          |

| 7  | V <sub>CMO</sub>    | 共模电压                | 71 | D <sub>Q5</sub>  | Q 路数据输出位 D <sub>Q5</sub>          |

| 8  | V <sub>CC</sub>     | 模拟电源                | 72 | D <sub>Q5</sub>  | Q 路数据输出位 D <sub>Q5</sub>          |

| 9  | GND <sub>A</sub>    | 模拟地                 | 73 | V <sub>DD</sub>  | 输出驱动电源                            |

| 10 | IN <sub>I-</sub>    | I 路模拟输入负            | 74 | GND <sub>D</sub> | 输出驱动地                             |

| 11 | IN <sub>I+</sub>    | I 路模拟输入正            | 75 | D <sub>Q6</sub>  | Q 路数据输出位 D <sub>Q6</sub>          |

| 12 | GND <sub>A</sub>    | 模拟地                 | 76 | D <sub>Q6</sub>  | Q 路数据输出位 D <sub>Q6</sub>          |

| 13 | V <sub>CC</sub>     | 模拟电源                | 77 | D <sub>Q7</sub>  | Q 路数据输出位 D <sub>Q7</sub><br>(最高位) |

| 14 | FSR/ST1             | 满刻度范围选/扩展控制<br>模式选择 | 78 | D <sub>Q7</sub>  | Q 路数据输出位 D <sub>Q7</sub><br>(最高位) |

| 15 | R                   | 时钟置位控制输入            | 79 | DOR              | 溢出同相输出                            |

| 16 | V <sub>CC</sub>     | 模拟电源                | 80 | DOR              | 溢出反相输出                            |

| 17 | V <sub>CC</sub>     | 模拟电源                | 81 | QCLK             | 数据时钟反相输出                          |

| 18 | INCLK+ <sup>+</sup> | 时钟输入正               | 82 | QCLK             | 数据时钟同相输出                          |

| 19 | INCLK- <sup>-</sup> | 时钟输入负               | 83 | DI7              | I 路数据输出位 D <sub>I7</sub><br>(最高位) |

| 20 | V <sub>CC</sub>     | 模拟电源                | 84 | DI7              | I 路数据输出位 D <sub>I7</sub><br>(最高位) |

| 21 | GND <sub>A</sub>    | 模拟地                 | 85 | DI6              | I 路数据输出位 D <sub>I6</sub>          |

| 22 | IN <sub>Q+</sub>    | Q 路模拟输入正            | 86 | DI6              | I 路数据输出位 D <sub>I6</sub>          |

| 23 | IN <sub>Q-</sub>    | Q 路模拟输入负            | 87 | GND <sub>D</sub> | 输出驱动地                             |

| 24 | GND <sub>A</sub>    | 模拟地                 | 88 | VDD              | 输出驱动电源                            |

| 25 | V <sub>CC</sub>     | 模拟电源                | 89 | DI5              | I 路数据输出位 D <sub>I5</sub>          |

| 26 | PD                  | 省电模式控制              | 90 | DI5              | I 路数据输出位 D <sub>I5</sub>          |

| 27 | GND <sub>A</sub>    | 模拟地                 | 91 | DI4              | I 路数据输出位 D <sub>I4</sub>          |

| 28 | V <sub>CC</sub>     | 模拟电源                | 92 | DI4              | I 路数据输出位 D <sub>I4</sub>          |

| 29 | PDQ                 | Q 路省电模式控制           | 93 | DI3              | I 路数据输出位 D <sub>I3</sub>          |

| 30 | CAL                 | 校正控制                | 94 | DI3              | I 路数据输出位 D <sub>I3</sub>          |

| 31 | VREF                | 基准输出                | 95 | DI2              | I 路数据输出位 D <sub>I2</sub>          |

| 32 | Rext                | 外接电阻                | 96 | DI2              | I 路数据输出位 D <sub>I2</sub>          |

|    |                  |                                    |     |                  |                                    |

|----|------------------|------------------------------------|-----|------------------|------------------------------------|

| 33 | V <sub>CC</sub>  | 模拟电源                               | 97  | GND <sub>D</sub> | 输出驱动地                              |

| 34 | Tdiode_p         | 温度二极管正级                            | 98  | NC               | 未连接                                |

| 35 | Tdiode_n         | 温度二极管负级                            | 99  | VDD              | 输出驱动电源                             |

| 36 | DQd0             | Q 路数据输出位 D <sub>Qd0</sub><br>(最低位) | 100 | DI1              | I 路数据输出位 D <sub>I1</sub>           |

| 37 | DQd0             | Q 路数据输出位 D <sub>Qd0</sub><br>(最低位) | 101 | DI1              | I 路数据输出位 D <sub>I1</sub>           |

| 38 | DQd1             | Q 路数据输出位 D <sub>Qd1</sub>          | 102 | DI0              | I 路数据输出位 D <sub>I0</sub><br>(最低位)  |

| 39 | DQd1             | Q 路数据输出位 D <sub>Qd1</sub>          | 103 | DI0              | I 路数据输出位 D <sub>I0</sub><br>(最低位)  |

| 40 | VDD              | 输出驱动电源                             | 104 | DID7             | I 路数据输出位 D <sub>Id7</sub><br>(最高位) |

| 41 | GND <sub>A</sub> | 模拟电源                               | 105 | DID7             | I 路数据输出位 D <sub>Id7</sub><br>(最高位) |

| 42 | GND <sub>D</sub> | 输出驱动地                              | 106 | DID6             | I 路数据输出位 D <sub>Id6</sub>          |

| 43 | DQd2             | Q路数据输出位D <sub>QD2</sub>            | 107 | DID6             | I 路数据输出位 D <sub>Id6</sub>          |

| 44 | DQd2             | Q路数据输出位D <sub>QD2</sub>            | 108 | GND <sub>D</sub> | 输出驱动地                              |

| 45 | DQd3             | Q路数据输出位D <sub>QD3</sub>            | 109 | NC               | 未连接                                |

| 46 | DQd3             | Q路数据输出位D <sub>QD3</sub>            | 110 | VDD              | 输出驱动电源                             |

| 47 | DQd4             | Q路数据输出位D <sub>QD4</sub>            | 111 | DID5             | I路数据输出位 D <sub>ID5</sub>           |

| 48 | DQd4             | Q路数据输出位D <sub>QD4</sub>            | 112 | DID5             | I路数据输出位 D <sub>ID5</sub>           |

| 49 | DQd5             | Q路数据输出位D <sub>QD5</sub>            | 113 | DID4             | I路数据输出位 D <sub>ID4</sub>           |

| 50 | DQd5             | Q路数据输出位D <sub>QD5</sub>            | 114 | DID4             | I路数据输出位 D <sub>ID4</sub>           |

| 51 | VDD              | 输出驱动电源                             | 115 | DID3             | I路数据输出位 D <sub>ID3</sub>           |

| 52 | NC               | 未连接                                | 116 | DID3             | I路数据输出位 D <sub>ID3</sub>           |

| 53 | GND <sub>D</sub> | 输出驱动地                              | 117 | DID2             | I路数据输出位 D <sub>ID2</sub>           |

| 54 | DQd6             | Q路数据输出位D <sub>QD6</sub>            | 118 | DID2             | I路数据输出位 D <sub>ID2</sub>           |

| 55 | DQd6             | Q路数据输出位D <sub>QD6</sub>            | 119 | GND <sub>D</sub> | 输出驱动地                              |

| 56 | DQd7             | Q路数据输出位D <sub>QD7</sub> (最<br>高位)  | 120 | NC               | 未连接                                |

| 57 | DQd7             | Q路数据输出位D <sub>QD7</sub> (最<br>高位)  | 121 | VDD              | 输出驱动电源                             |

|    |                  |                         |     |                  |                                |

|----|------------------|-------------------------|-----|------------------|--------------------------------|

| 58 | DQ0              | Q路数据输出位 $D_{QD0}$ (最低位) | 122 | DID1             | I路数据输出位 $D_{ID1}$              |

| 59 | DQ0              | Q路数据输出位 $D_{QD0}$ (最低位) | 123 | DID1             | I路数据输出位 $D_{ID1}$              |

| 60 | DQ1              | Q路数据输出位 $D_{I1}$        | 124 | DID0             | I路数据输出位 $D_{ID0}$              |

| 61 | DQ1              | Q路数据输出位 $D_{I1}$        | 125 | DID0             | I路数据输出位 $D_{ID0}$              |

| 62 | VDD              | 输出驱动电源                  | 126 | QCAL             | 校正运行指示输出                       |

| 63 | NC               | 未连接                     | 127 | CalDly /DES /ST2 | 上电校正延迟选择/<br>双沿采样控制/<br>串行接口选通 |

| 64 | GND <sub>D</sub> | 输出驱动地                   | 128 | V <sub>cc</sub>  | 模拟电源                           |

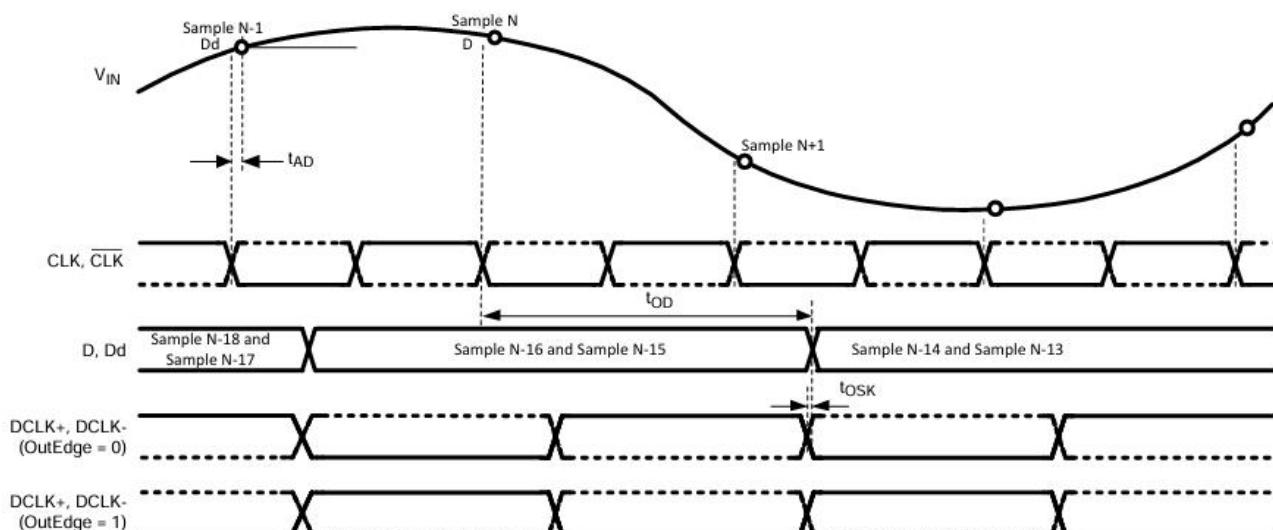

## 时序图

图 2. CD08AD1500 单数据速率(SDR)时序 (OutEdge 为高或低)

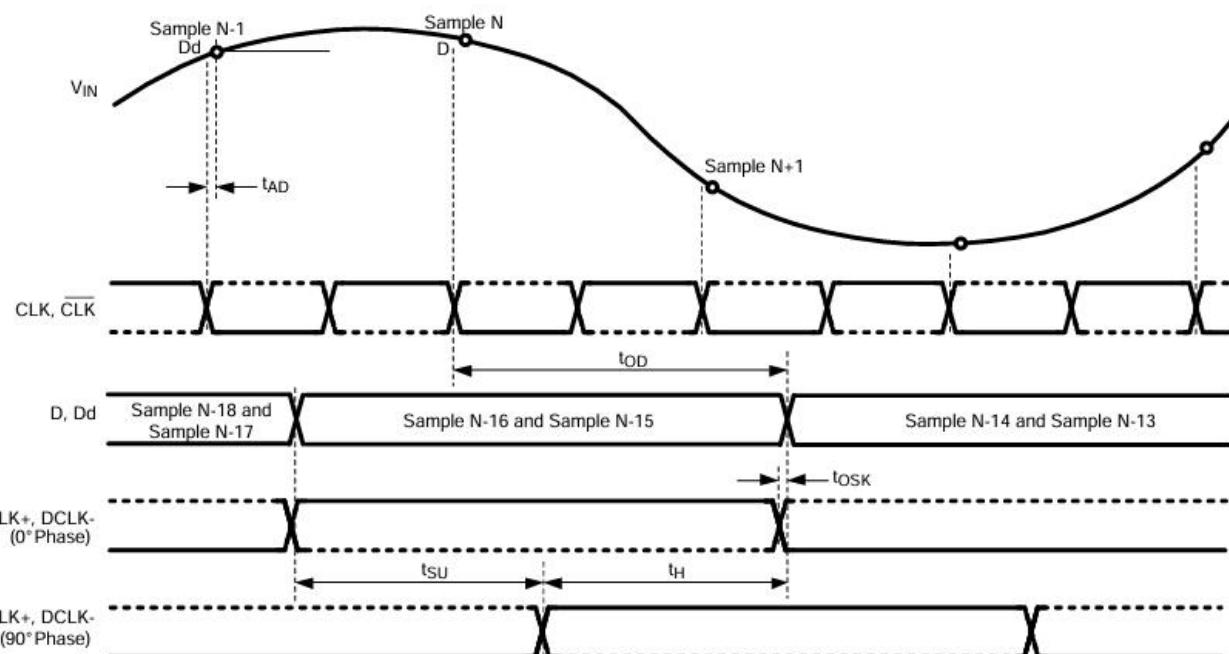

图 3.CD08AD1500 双倍数据速率(DDR)时序 (OutEdge 悬空或  $V_{CC}/2$ )

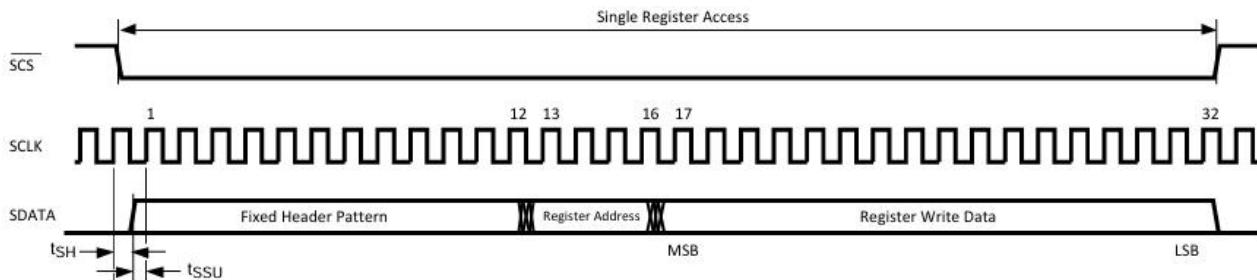

图 4.串行接口时序

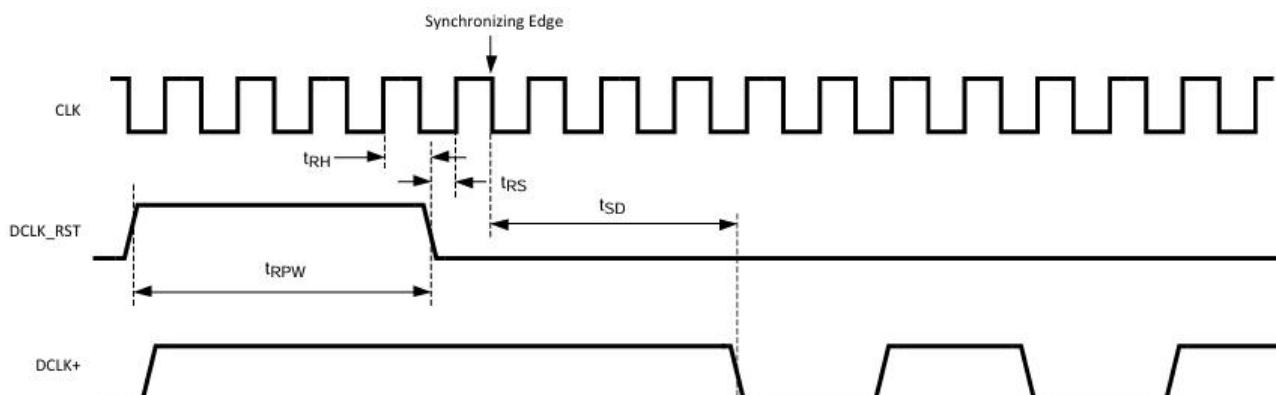

图 5.OutEdge 悬空或  $V_{CC}/2$  时, DDR 模式的时钟重置时序

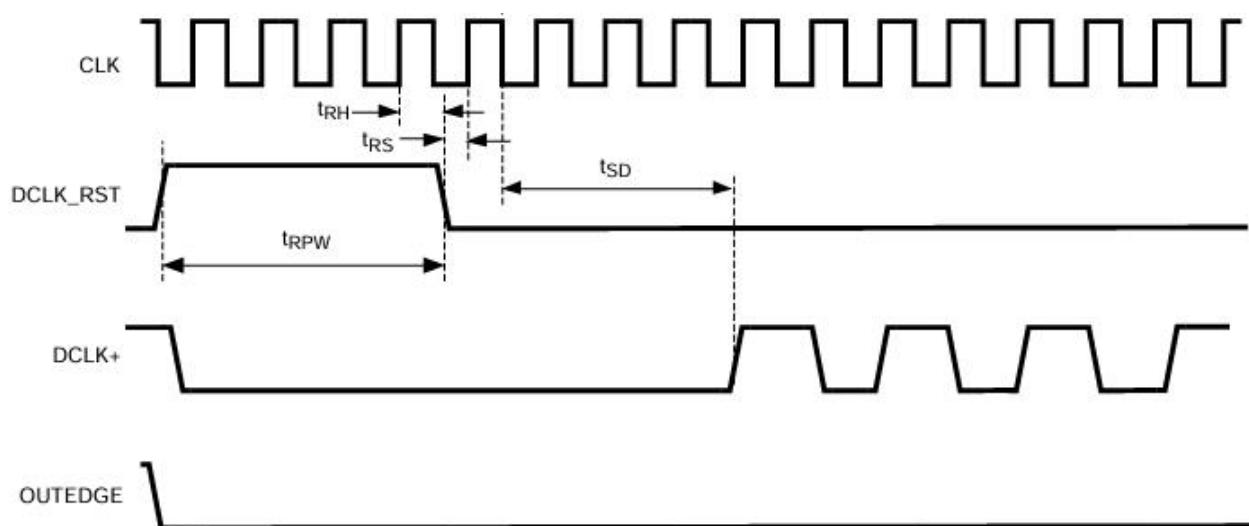

图 6. OutEdge 为低时, SDR 模式的时钟重置时序

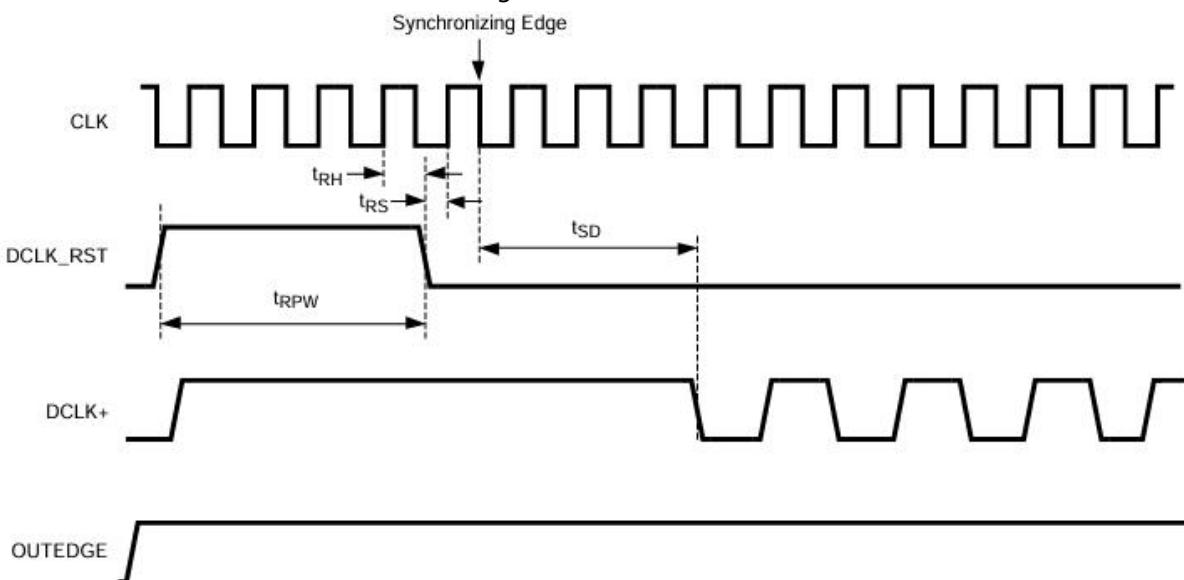

图 7. 为高时, SDR 模式的时钟重置时序

图 8. 自校正和指令校正时序

## 输出码

表 1. 输出码 (标准模式, FSR 为高)

| 等效十进制 | VIN+ - VIN- | 电压电平                | 二进制码     | 溢出位 |

|-------|-------------|---------------------|----------|-----|

| 255   | >460mV      | >正满度范围 +<br>1/2LSB  | 11111111 | 1   |

| 255   | 460mV       | 正满度范围 + 1/2LSB      | 11111111 | 0   |

| 254   | 458mV       | 正满度范围 - 1/2LSB      | 11111110 | 0   |

| .     | .           | .                   | .        |     |

| .     | .           | .                   | .        |     |

| 128   | 1.8mV       | 双极 0 + 1/2LSB       | 10000000 | 0   |

| 127   | -1.8mV      | 双极 0 - 1/2LSB       | 01111111 | 0   |

| .     | .           | .                   | .        |     |

| .     | .           | .                   | .        |     |

| 1     | -458mV      | 负满度范围 +<br>1/2LSB   | 00000001 | 0   |

| 0     | -460mV      | 负满度范围 - 1/2LSB      | 00000000 | 0   |

| 0     | < -460mV    | < 负满度范围 +<br>1/2LSB | 00000000 | 1   |

## 推荐工作条件

- 电源电压 ( $V_{CC}, V_{DD}$ ) : 1.8V-2.0V

- 模拟输入共模电压 : 1.26V ±50mV

- 差分模拟输入范围 : 570-1100 mVpp

- 串行接口时钟输入频率 : 100MHz

- 时钟频率范围 : 200 MHz ~ 1500MHz

- 时钟输入占空比 : 20%-80% (Typical 50%)

- 差分时钟输入幅度 : 0.5-2.0 V<sub>PP</sub> (Typical 0.6 V<sub>PP</sub>)

- 工作温度 : -45 ~85 C

## 推绝对最大额定值

- 电源电压 ( $V_{CC}, V_{DD}$ ): 2.2V

- 电源差  $V_{DD}-V_{CC}$ : 0V ~ 100mV

- 任意引脚的输入电流 :  $\pm 25mA$

- ESD 保护 : 人体模型 : 2000V, 机械模型 : 250V

- 引线耐焊接温度  $TH(10s)$ : 300 °C

- 贮存温度  $T_S$ : - 65 °C ~ 150 °C

- 结温  $T_J$ : 175 °C

## 性能参数

除另有规定外, 电特性应按表 2 的规定。电测试方法按 SJ 20961-2006 的规定。模拟输入交流耦合, 差分 920mVpp; 时钟交流耦合输入, 占空比 50%; 外接电阻  $R_{ext}=3300\Omega \pm 0.1\%$ 。表 3 的典型值仅为 25°C 下参考数据。

| 参数名称     | 符号            | 条件(除另有规定外, $VCC=VDD = 1.9V$ ) | MIN  | TYP       | MAX  | Unit  |

|----------|---------------|-------------------------------|------|-----------|------|-------|

| 分辨率      | RES           |                               | 8    |           |      | bits  |

| 模拟电源电流   | $I_{CC}$      | $PD = PDQ = 0V$               | --   | 900       | 930  | mA    |

| 数字电源电流   | $I_{DD}$      | $PD = PDQ = 0V$               | --   | 220       | 250  | mA    |

| 功耗       | PD            | $PD = PDQ = 0V$               | --   | 2.0       | 2.2  | W     |

| 积分非线性误差  | $E_L$         | DC Coupled, 1MHz              | -1.2 | $\pm 0.6$ | 1.2  | LSB   |

| 微分非线性误差  | $E_{DL}$      | Sine Wave Overranged          | -1.0 | $\pm 0.4$ | 1.0  | LSB   |

| 失调误差     | $E_O$         |                               | -2.5 | -0.45     | -2.5 | LSB   |

| 正满刻度误差   | $E_{FS+}$     |                               | -40  | $\pm 10$  | 40   | mV    |

| 负满刻度误差   | $E_{FS-}$     |                               | -40  | $\pm 10$  | 40   | mV    |

| 带隙基准输出电压 | $V_{REF}$     | $I_{REF} = \pm 100\mu A$      | 1.20 | 1.27      | 1.33 | V     |

| 模拟差分输入电压 | $V_{ID1(PP)}$ | FSR 脚 14 is low               | 570  | 700       | 900  | mVp-p |

|          |               | FSR 脚 14 is high              | 790  | 920       | 1100 | mVp-p |

| 模拟差分输入电阻 | RI            |                               | 94   | 100       | 106  | Ω     |

| 时钟输入差分电压 | $V_{ID2(PP)}$ |                               | 0.5  | 0.6       | 2    | V     |

| 逻辑输入低电平  | $V_{IL}$      | Outv, R, PD, PDQ              | --   |           | 0.3  | V     |

| 逻辑输入高电平  | $V_{IH}$      |                               | 1.6  |           | --   | V     |

|                 |               |                                       |      |           |      |        |

|-----------------|---------------|---------------------------------------|------|-----------|------|--------|

| 数字输出高电平         | $V_{OH}$      | $Q_{Cal}$ (126 引脚)                    | 1.5  | 1.65      | --   | $V$    |

| 数字输出低电平         | $V_{OL}$      |                                       | --   | 0.15      | 0.3  | $V$    |

| LVDS 差分输出电压     | $V_{OD (PP)}$ | OutV= $V_{CC}$ , $V_{REF}$ 悬空         | 400  | 700       | 1000 | $mV$   |

|                 |               | OutV= GND, $V_{REF}$ 悬空               | 280  | 500       | 800  | $mV$   |

| 溢出输出码           | OROC          | $(V_{IN+}-V_{IN-}) > +$ 满度            | 255  | --        | --   | --     |

|                 |               | $(V_{IN+}-V_{IN-}) < -$ 满度            | --   | --        | 0    | --     |

| 增益平坦度           | $\Delta A$    | dc ~ 500MHz                           | -1   | $\pm 0.5$ | 1    | $dBFS$ |

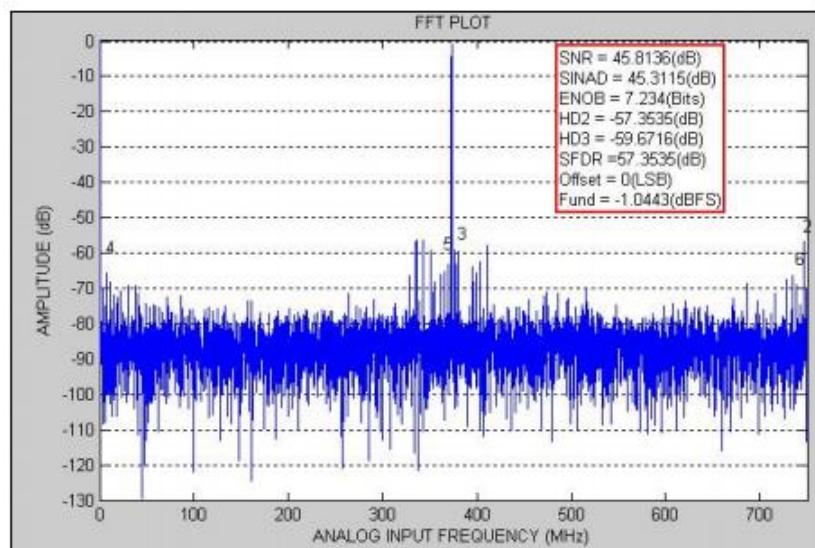

| 信噪比             | SNR           | $f_{CLK}=1.5GHz$ ,<br>$f_{IN}=373MHz$ | 42   | 45.0      | --   | $dB$   |

| 有效位             | ENOB          |                                       | 6.6  | 7.2       | --   | Bits   |

| 信噪失真比           | SINAD         | $f_{CLK}=1.5GHz$ ,<br>$f_{IN}=373MHz$ | 41.5 | 44.5      | --   | $dB$   |

| 无杂散动态范围         | SFDR          |                                       | 45   | 54        | --   | $dB$   |

| 总谐波失真           | THD           | $f_{CLK}=1.5GHz$ ,<br>$f_{IN}=373MHz$ | --   | --        | -45  | $dB$   |

| 最大转换速率          | $S_{Rmax}$    | $f_{IN} = 373MHz$                     | 1.5  | --        | --   | $GSPS$ |

| 输出时钟占空比         | $Q_{DC}$      |                                       | 45   | 50        | 55   | %      |

| 时钟置位脉冲宽度        | $t_{RPW}$     | 见图. 5~7 时序                            | 4    | --        | --   | 时钟周期   |

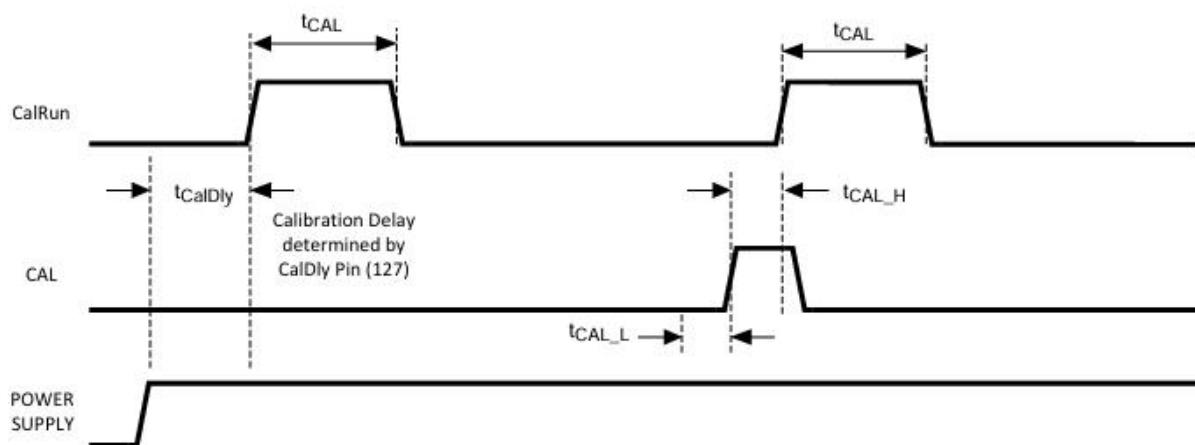

| 校正控制输入<br>低电平时间 | $t_{CAL\_L}$  | 见图. 8 时序                              | 80   | --        | --   | 时钟周期   |

| 校正控制输入<br>高电平时间 | $t_{CAL\_H}$  | 见图. 8 时序                              | 80   | --        | --   | 时钟周期   |

## 典型特性曲线图

$f_{clk}=1.5\text{GSPS}$ ,  $f_{IN}=373\text{MHz}$

$f_{clk}=1.5\text{GSPS}$ ,  $f_{IN}=373\text{MHz}$

## 应用说明

### 1. 功能描述

#### 1) .概述

CD08AD1500 采用了带校正的折叠内插结构，可以达到 7.1bit 的有效位。折叠运放的应用极大地减

少了比较器的数量和功耗。内插结构减少了前置运放的数量，同时减少了输入信号的负载电容，更进一步降低了功耗。除此以外，器件集成校正降低了因折叠结构引起的 INL 弓形。通过这些技术实现了超高速、高性能、低功耗的转换器。

在转换器输入电压范围内的模拟输入信号被数字化为 8 位码值输出，转换速率为 200MSPS ~ 1.5GSPS。典型情况下差分输入电压低于负的满刻度值将使输出码值全为 0；差分输入电压高于正的满刻度值将使输出码值全为 1。“I”或“Q”通道出现上面两个中任一种情况将会溢出输出范围，这些单个的输出码值超出范围指的是从一个通道或两个通道输出的码值低于负的满刻度值或超出正的满刻度值。两通道转换器都有一个满足两路 LVDS 输出总线的 1:2 多路信号分离器，这些输出总线上的数据在每条总线上以采样率一半的速率输出，同时使用者可以选择隔行扫描来达到采样率的速率输出。

输出幅度可以选择普通模式或者低幅度模式。采用低幅度模式可以降低功耗但会造成一些或所有的数据采集，特别是在高采样率和边界设计系统下。

#### a. 自校正

上电和用户指令都可以启动自校正。自校正主要用来修调 100Ω 模拟输入差分终端电阻，同时最小化满刻度误差、失调误差、DNL 和 INL，最大化 SNR、THD、SINAD 和 ENOB，同样内部偏置电流也是通

过自校正过程来进行设置。上电自校正和用户指令启动自校正都可以实现这些目的。自校正是器件功能的一个重要组成部分，其目的是使器件达到更好的性能。自校正除了在上电启动外，只要 FSR 引脚（14 脚）的控制发生变化就要重新启动自校正。为了达到更好的性能，我们建议在上电之后和器件工作温度相对与系统性能要求的温度差别很大时，让自校正运行 20 秒或更长时间。更详细的可参考 2.4).b.②指令校正。当器件处于省电模式（PD 或 PDQ 为高）时，自校正不能初始化或者运行。更详细的信息可参考 1.1).g 省电模式自校正与省电模式的关系。

在普通工作模式下，器件上电和输入一个有效的校正指令，自校正都会工作。校正指令保持 CAL 引脚（30 脚）为低至少一个 tCAL\_L 时钟周期，接着保持 CAL 引脚为高至少另一个 tCAL\_H 时钟周期，其中 tCAL\_L 和 tCAL\_H 在转换器电特性中定义的，见图 8。自校正所占有的时间为转换器电特性中定义的 tCAL。在上电之后保持 CAL 引脚为高将阻止自校正过程运行，直到 CAL 引脚出现前面提到的 tCAL\_L 时钟周期紧跟着是 tCAL\_H 时钟周期。

CalDly（引脚 127）用来选择在上电之后到自校正开始运行时的 2 个延迟时间之中的 1 个，自校正的延迟时间由 CalDly 引脚设置，在转换器电特性中定义为 tCalDly，见表 3 所示。这些延迟时间的长度为电源电压上电并稳定到自校正工作这段时间。在上电之后如果 PD（26 脚）这个引脚为高，自校正延

迟计算器将会无效，直到 PD 引脚重新为低。因此，在上电后保持 PD 引脚为高，将进一步延迟上电后自校正周期的开始。CalDly 引脚最好的设置依赖于电源电压的上电设置时间。

表 3. 上电延迟时间控制功能表(PD 为低电平)

| CalDly (引脚 127) | 上电延迟选择 ( $t_{CalDly}$ ) |

|-----------------|-------------------------|

| H               | 231个输入时钟周期              |

| L               | 231个输入时钟周期              |

| DES(双沿采样模式)     | 231个输入时钟周期              |

### 自校正工作注意事项：

- 在自校正周期期间，溢出 (QOR) 输出可能是校正算法的一个有用结果。在校正期间，所有数据输出和溢出输出的数据是无效的。

- 在上电校正期间和指令校正期间，内部 ADC 核的时钟和输出时钟 QCLK 停止工作；这时输入终端电阻阻值被修调到  $R_{ext}/33$ 。在校正周期中校正输入电阻是校正期间的一部分，目的是为了减少噪声。参考 2.4) .b. 自校正。这个外接电阻位于引脚 32 与地之间， $R_{ext}$  必须精确等于  $3300\Omega \pm 0.1\%$ 。利用这个值，输入终端电阻阻值被修调为  $100\Omega$ 。因为  $R_{ext}$  还用来为采样/保持运放、前置放大器和比较器设置适当的偏置电流，所以  $R_{ext}$  的其它值不能采用。

- 只要校正在运行，无论是上电自校正还是用户指令启动自校正，CalRun 输出都为高。

#### b. 输出数据的捕获

在时钟 INCLK+ (引脚 18) 的下降沿数据输出，即在 13 个输入时钟周期后 DI 和 DQ 端输出的数据和在 14 个输入时钟周期后 DId 和 DQd 端输出的数据有效。输出数据在输出获得之前，有另外的内部延迟叫 tOD，见时序图。只要有输入时钟信号，CD08AD1500 就会进行数据转换工作。全差分比较器设计和创新的采样保持放大器设计，以及自校正技术，在 1.5GHz 以下获得了一个非常平坦的 SINAD/ENOB 响应。CD08AD1500 输出数据信号是 LVDS，输出格式是二进制偏移码。

#### c. 控制模式

提供的多个控制引脚实现了用户控制的多种模式。例如包括校正循环的初始化，省电模式和满刻度范围设置控制。然而，CD08AD1500 也提供一个扩展控制模式，通过扩展控制模式，一个串行接口被用来访问基于寄存器的许多高级特性的控制。这个扩展控制模式不能自动被使用，而使用者希望在所有时间都能用普通控制模式或者扩展控制模式。当器件处于扩展控制模式时，基于引脚控制的许多特性就会被基于寄存器控制的特性所取代，那些基于引脚的控制将无效。这些引脚是 Outv (引脚 3), OutEdge/DDR (引脚 4), FSR (引脚 14) 和 CalDly/DES (引脚 127)，见表 4 所示。关于扩展控制模式更详细的信息请参考 1.2) 普通/扩展控制模式。

表 4. 控制模式

| 控制输入           | 功能脚  |                    |                  |                  |

|----------------|------|--------------------|------------------|------------------|

| FSR/ST (引脚 14) | 控制模式 | CalDly/DES/ST2 (引脚 | OutEdge/DDR/DATA | Outv/SCLK (引脚 3) |

|                      |      | 127)                                                          | (引脚 4)                                                 |                                          |                     |

|----------------------|------|---------------------------------------------------------------|--------------------------------------------------------|------------------------------------------|---------------------|

| H 或 L<br>(VCC 或 GND) | 普通模式 | 上电校正延迟选择:<br>H 时延迟 231 个时钟周期; L 时延迟 225 个时钟周期双沿采样: 悬空或 0.5VCC | 单数据速率模式 (SDR) :<br>为 H 或 L 双倍数据速率模式 (DDR) : 悬空或 0.5VCC | 控制 LVDS 输出幅度:<br>H 时输出正常幅度;<br>L 时输出幅度降低 |                     |

| 悬空或 VCC/2            | 扩展模式 | 选通扩展模式串行接口的时钟和数据                                              | H<br>L                                                 | 串行数据输入被封锁<br>串行数据输入                      | 串行时钟输入被封锁<br>串行时钟输入 |

#### d.模拟输入

CD08AD1500 必须由一个差分输入信号驱动, 单端信号工作不是推荐的。交流耦合输入时, VCMO (7 引脚) 接地; 当直流耦合输入时, VCMO 引脚悬空, 但输入共模电压必须等于 VCMO 的输出电压。引脚 14 (FSR) 提供了 2 个满刻度范围设置, 在普通模式下, 由 FSR 设置来控制输入满刻度范围, 通过转换器电特性中参数模拟输入范围来定义的, 满刻度范围设置时对两个 ADC 都有效。在扩展控制模式, 输入满刻度范围由串行接口的数据输入进行调节, 在 1.4) 和 2.2) 中进行叙述。模拟输入满刻度范围控制见表 5。

表 5 模拟输入满刻度范围控制表

| FSR                    | 模拟差分输入满刻度范围                                    |

|------------------------|------------------------------------------------|

| H                      | 790 ~ 1100 mVpp, 920 mVpp (typ)                |

| L                      | 570 ~ 900 mVpp, 700 mVpp (typ)                 |

| 悬空或 V <sub>CC</sub> /2 | 串行接口的 9 位二进制码输入控制, 560 ~ 840 mVpp, 默认 700 mVpp |

#### e.时钟输入/输出

CD08AD1500 必须由一个差分时钟信号通过交流耦合连接来驱动, 2.3) 描述了时钟输入引脚的用法。一个差分 LVDS 输出时钟用来锁存 ADC 输出数据, 便于后续器件接收数据。

CD08AD1500 提供了两种输出时钟选择, 一种是选择输出数据在输出时钟 QCLK 的上沿转换还是在输出时钟的下沿转换, 另一种选择是单数据速率 (SDR) 输出, 还是双数据速率 (DDR) 输出, 见表 6, 时序见图 2、图 3。

表 6 输出时钟选择 (FSR 为 H 或 L)

| OutEdge/DDR (4 引脚) | 模式  | 输出时钟                        |

|--------------------|-----|-----------------------------|

| H                  | SDR | 频率为 1/2 输入频率, 输出数据在该时钟的上沿转换 |

|                |     |                            |

|----------------|-----|----------------------------|

| L              |     | 频率为 1/2 输入频率，输出数据在该时钟的下沿转换 |

| 悬空或 $V_{CC}/2$ | DDR | 频率为 1/4 输入频率，输出数据在该时钟的上沿转换 |

CD08AD1500 时钟输入内部有一个占空比调节器，以改善内部时钟性能，可通过扩展模式(地址码 0001)进行选择，使占空比调节器是否工作，默认设置是工作的。占空比调节器允许 ADC 的时钟可以是一个占空比为 20~80% (最差情况) 的信号源。

### ①. 双沿采样(DES 功能)

DES 模式允许 CD08AD1500 中的一个输入 (I 或 Q 通道) 被两个 ADC 所采样。一个 ADC 在输入时钟的正边沿采样输入信号，另一个 ADC 在输入时钟的负边沿采样输入。因此信号输入在每个时钟周期被采样两次，所以一个完整的采样率是输入时钟频率的两倍，或者对于 1.5GHz 的输入时钟采样率为 3GSPS。在这个模式，交替存取的输出数据被一个多路选择器转换为 1:4。由于采样率是二倍，在 1.5GHz 输入时钟下，4 路数据输出中的任一路都以 750MHz 的速率输出，所有数据都是并行输出。每个时钟输出的 4 路并行数据是紧跟着采样顺序的，从最早到最后依次是：DQd、DI<sub>d</sub>、DQ、DI，即最早是 DQd，其次是 DI<sub>d</sub>，最后是 DI；这表示可以提供不同采样率的可能性。

双沿采样在普通控制模式下，只有 “I” 路模拟输入(INI)可用，“Q” 路模拟输入(INQ)不用。在扩展控制模式，用户可以选择任意 1 个 (“I” 或 “Q”) 作为模拟输入被采样，地址码为 1110。控制功能见表 7。CD08AD1500 包括一个自动时钟相位后台校正特性，这个特性能在 DES 模式下自动的连续用来调节 I 通道和 Q 通道的时钟相位。这个特性免除了手动设置时钟相位的需要，同时提供最佳的双边沿采样 ENOB 性能。

**特别注意：**在 DES 模式下的后台校正特性不能代替在进入 DES 模式之前要运行的指令校正，或如果芯片工作环境温度出现大的变化时所需要的指令校正。

表 7 输出数据对应的输入通道采样时间

| 数据输出（总是对应 $Q_{CLK}$ 的下降沿）  | 普通采样模式                                      | 双沿采样模式 (DES)                                  |                                               |

|----------------------------|---------------------------------------------|-----------------------------------------------|-----------------------------------------------|

|                            |                                             | 选择 I 通道输入                                     | 选择 Q 通道输入*                                    |

| D <sub>I</sub>             | “I” 输入采样对应输出前 13 个 IN <sub>CLK</sub> 周期的下降沿 | “I” 输入采样对应输出前 13 个 IN <sub>CLK</sub> 周期的下降沿   | “Q” 输入采样对应输出前 13 个 IN <sub>CLK</sub> 周期的下降沿   |

| D <sub>I<sub>d</sub></sub> | “I” 输入采样对应输出前 14 个 IN <sub>CLK</sub> 周期的下降沿 | “I” 输入采样对应输出前 14 个 IN <sub>CLK</sub> 周期的下降沿   | “Q” 输入采样对应输出前 14 个 IN <sub>CLK</sub> 周期的下降沿   |

| D <sub>Q</sub>             | “Q” 输入采样对应输出前 13 个 IN <sub>CLK</sub> 周期的下降沿 | “I” 输入采样对应输出前 13.5 个 IN <sub>CLK</sub> 周期的下降沿 | “Q” 输入采样对应输出前 13.5 个 IN <sub>CLK</sub> 周期的下降沿 |

| D <sub>Qd</sub>            | “Q” 输入采样对应输出前 14 个 IN <sub>CLK</sub> 周期的下降沿 | “I” 输入采样对应输出前 14.5 个 IN <sub>CLK</sub> 周期的下降沿 | “Q” 输入采样对应输出前 14.5 个 IN <sub>CLK</sub> 周期的下降沿 |

\*在 DES 普通模式下，只有 I 通道进行采样。在 DES 的扩展模式下，I 或 Q 通道都可以进行采样。

## ②.OutEdge 引脚设置

为了使在 SDR 模式数据采样变得容易，输出数据可以在输出数据时钟 (QCLK) 的正沿或负沿进行转换。这可以通过 OutEdge 输入 (引脚 4) 来选择。OutEdge 输入为高时输出数据在 QCLK 上升沿转换；OutEdge 输入为低时输出数据在 QCLK 下降沿转换，见表 6。参考 2.4) .c 输出沿同步。

## ③.双倍数据速率

提供了单倍数据率 (SDR) 或双倍数据率 (DDR) 输出的选择。如果是 SDR，输出时钟 (QCLK) 频率与两路输出总线的数据速率一样。如果是 DDR，QCLK 频率是数据速率的一半，数据在 QCLK 的两个沿被送到输出端。DDR 时钟通过让引脚 4 悬空或 VCC/2 来控制，在 FSR (引脚 14) 普通控制模式有效，见表 4 和表 6。

## f.LVDS 输出

数据输出、溢出输出(DOR)和时钟输出 (QCLK) 都是 LVDS。当 Outv 输入 (引脚 3) 为高时，输出电流源将提供 3mA 的输出电流到 100Ω的差分电阻负载；当 Outv 输入 (引脚 3) 为低时，输出电流源将提供 2.2mA 的输出电流到 100Ω的差分电阻负载，见表 8。为了缩短 LVDS 线长和降低系统噪声，Outv 输入 (引脚 3) 为低会获得满意的性能，同时降低功耗。如果 LVDS 路线太长或 CD08AD1500 系统噪声太大，把 Outv 输入接高电平是很有必要的。

当 VREF (引脚 31)未连接或悬空时，LVDS 数据输出有一个 800mV 的共模电压。如果要求更高的共模电压，可以通过把 VREF 引脚与 VCC 相连使共模电压增加到 1.2V，见表 9。

**特别注意：**连接 VREF 引脚到 VCC 也会增加差分 LVDS 输出电压 40mV。

表 8. LVDS 输出共模电压

| Outv 输入(引脚 3) | LVDS 输出幅度                     |

|---------------|-------------------------------|

| H             | 400 ~ 1000mVpp, 700 mVpp(typ) |

| L             | 280 ~ 800mVpp, 500 mVpp(typ)  |

表 9. LVDS Output Common Mode Voltage (VOS)

| VREF (引脚 31) | LVDS 输出幅度   |

|--------------|-------------|

| H            | 1.2V(typ)   |

| L            | 800mVp(typ) |

## g.省电模式 (Power Down)

当 PD(引脚 26)为低时，CD08AD1500 处于正常工作状态。当 PD 引脚为高时，器件处于省电模式。在省电模式，数据输出引脚 (正和负) 都是三态，同时器件功耗被降低到最小。时钟输出 (QCLK 和

QCLK) 和溢出输出 (DOR 和 DOR) 不是三态，他们在内部被拉到地。因此，当 I 和 Q 都是省电模式时，时钟输出和溢出输出不能接到一个直流电压。

PDQ 引脚为高或悬空时将使 “Q” 通道处于省电模式，“I” 通道处于正常工作状态，不受 PDQ 的控制，见表 10。再回到普通工作模式，通道中将包含无意义的信息。如校正在运行期间 PD 置为高，器件不会进入省电工作，仍然正常工作，直至校正时序完成。然而，如果在已经上电和 PD 已为高的情况下，器件进入省电工作，不进行校正，直到 PD 变为低。如果器件处于省电模式要求手动校正，校正根本就不会启动。那就是说，手动校正输入完全被省电状态封锁了。但如果 PDQ 为高 “Q” 通道处于省电模式 “I” 通道校正仍会运行，“Q” 通道将不能被校正。如果 “Q” 通道是后来被使用，在 PDQ 为低后进行一次校正是必须的。

表 10. 省电模式控制

| 省电模式控制 |       | 工作模式 |      |

|--------|-------|------|------|

| PD     | PDQ   | I 路  | Q 路  |

| H      | H 或 L | 省电模式 | 省电模式 |

| L      | H 或悬空 | 正常工作 | 省电模式 |

|        | L     | 正常工作 | 正常工作 |

## 2) .普通/扩展控制

CD08AD1500 可以工作在这两种模式中任一种。普通的标准控制模式，使用者可以通过几个引脚来设置和控制器件的工作状态；“扩展控制模式”是通过一个串行接口和对 9 个寄存器的设置来实现另外的配置和控制选择。两种控制模式通过引脚 14 (FSR/ST1：满刻度范围选择和扩展控制模式选择) 来选择。控制模式的选择必须是一个固定的选择，当器件工作时不能随意转换这两种模式。表 11 显示了器件特性受控制模式选择的影响。

表 11. 器件特性和模式

| 特性                                   | 普通控制模式                                                    | 扩展控制模式                                                            |

|--------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|

| SDR 或 DDR 模式时钟                       | 引脚 4 悬空或 V <sub>CC</sub> /2 选择 DDR 时钟，为高或低选择 SDR 时钟       | 在配置寄存器 (1h; D10) 中用 nDE 选择。<br>当器件处于 DDR 模式，设置地址 1h, bit-8 必须为 0。 |

| DDR 模式时钟相位                           | 没有选择，只有 0°相位                                              | 在配置寄存器 (1h; D11) 中，用 DCP 选择。                                      |

| SDR 模式，数据转换在 Q <sub>CLK</sub> 上升或下降沿 | 当引脚 4 为高时，SDR 数据在 Q <sub>CLK+</sub> 上升沿转换；当引脚 4 为低时，下降沿转换 | 在配置寄存器 (1h; D8) 中，用 OE 选择                                         |

|             |                                                  |                                                                         |

|-------------|--------------------------------------------------|-------------------------------------------------------------------------|

| LVDS 输出幅度   | 引脚 3 为高，正常的差分数据和 Q <sub>CLK</sub> 输出幅度；为低时，减小幅度。 | 在配置寄存器 (1h; D9) 中，用 OV 选择                                               |

| 上电校正延迟      | 当引脚 127 为低，选择短的延迟；为高，选择长的延迟。                     | 只能短的延迟                                                                  |

| 满刻度范围       | 当引脚 14 为高时，正常的输入满刻度范围；为低时，减小范围。范围的选择对两个通道均有效。    | 在 1.4 寄存器描述中，整个正常满刻度范围内多达 512 步长的调节。选择用输入满刻度范围调节寄存器 (3h; D7 ~ D15)      |

| 输入失调调节      | 不能调节                                             | 用输入失调寄存器 (2h; D7 ~ D15) 调节，多达 512 步长                                    |

| 双边沿采样选择     | 引脚 127 悬空或 V <sub>CC</sub> /2                    | 通过 DES 使能寄存器来控制                                                         |

| 双边沿采样输入通道选择 | 只有 I 通道输入可用                                      | I 或 Q 通道输入都可以被 2 个 ADC 采样                                               |

| DES 采样时钟调节  | 时钟相位是自动调节                                        | 在 DES 中设置 D14 使能寄存器 (Dh) 来选择自动时钟相位控制。时钟相位也可以通过粗和细寄存器 (Eh 和 Fh) 来进行手动调节。 |

扩展控制模式的默认状态由上电复位进行设置，如表 12 所示。

表 12. 扩展控制模式工作(14 脚悬空或 V<sub>CC</sub>/2)

| 特性             | 扩展控制模式默认状态          |

|----------------|---------------------|

| SDR 或 DDR 模式时钟 | DDR 模式时钟            |

| DDR 模式时钟相位     | QCLK 边沿 (0°相位) 数据变化 |

| LVDS 输出幅度      | 正常幅度 (700mVpp)      |

| 上电校正延迟         | 缩短的延迟               |

| 模拟输入满刻度范围      | 两个通道都是 700mVpp      |

| 输入失调调节         | 两个通道都没有失调调节         |

| 双边沿采样 (DES)    | 不用此模式               |

### 3) .串行接口

只有当器件工作在扩展控制模式下，3 线串行接口才能被激活。这些串行接口的引脚是串行时钟 (SCLK)、串行数据 (DATA) 和串行接口选择 (ST2)，八个只写寄存器通过串行接口获取信号。

ST2：通过串行接口访问一个寄存器时，这个信号应该为低。相对于 SCLK 的建立时间和保持时间必须满足要求。SCLK：串行数据输入在这个信号的上升沿获得，对 SCLK 没有最小频率要求。

DATA：每个寄存器存取要求这个输入端为一个明确的 32 位组合格式。这个格式由头模式、寄存器地址和寄存器值组成，寄存器值由 MSB 位开始。相对于 SCLK 的建立时间和保持时间必须满足要求，看时序图。

每个寄存器访问由 32 位组成，如图 4 所示的时序图。固定头模式为 0000 0000 0001 (11 个 0, 1 个 1)，写入次序是 0 最先写入，这 12 位组成头模式。接下来写入 4 位寄存器的地址，最后 16 位数据被写入到寄存器，不同寄存器的地址详细表述如表 13 所示。

当 ST2 永久保持为低电平时，从第 33 个 SCLK 开始后面的寄存器存取能直接完成，在寄存器地址之间不再进行选通。虽然这种用法不推荐，但那是可能的。

**重要提示：**当校正 ADC 的时候，串行接口不要使用，如果使用会降低器件的性能，除非再进行正确的校正。寄存器存取期间进行串行接口寄存器操作也会降低 ADC 的动态特性。

表 13. Register Address

| 4-bit 地址                                      |    |    |    |     |             |

|-----------------------------------------------|----|----|----|-----|-------------|

| 地址写入顺序：A3 在 H0 (固定头模式的最后位，即“1” ) 后锁存，A0 在最后锁存 |    |    |    |     |             |

| A3                                            | A2 | A1 | A0 | Hex | 寄存器地址       |

| 0                                             | 0  | 0  | 0  | 0h  | 保留          |

| 0                                             | 0  | 0  | 1  | 1h  | 状态配置        |

| 0                                             | 0  | 1  | 0  | 2h  | I 通道输入失调调节  |

| 0                                             | 0  | 1  | 1  | 3h  | I 通道满刻度电压调节 |

| 0                                             | 1  | 0  | 0  | 4h  | 保留          |

| 0                                             | 1  | 0  | 1  | 5h  | 保留          |

| 0                                             | 1  | 1  | 0  | 6h  | 保留          |

| 0                                             | 1  | 1  | 1  | 7h  | 保留          |

|   |   |   |   |    |             |

|---|---|---|---|----|-------------|

| 1 | 0 | 0 | 0 | 8h | 保留          |

| 1 | 0 | 0 | 1 | 9h | 保留          |

| 1 | 0 | 1 | 0 | Ah | Q 通道输入失调调节  |

| 1 | 0 | 1 | 1 | Bh | Q 通道满刻度电压调节 |

| 1 | 1 | 0 | 0 | Ch | 保留          |

| 1 | 1 | 0 | 1 | Dh | DES 使能      |

| 1 | 1 | 1 | 0 | Eh | DES 粗调节     |

| 1 | 1 | 1 | 1 | Fh | DES 细调节     |

## 注意事项

- 1、引脚 32 外接电阻 Rext 必须精确等于  $3300\Omega \pm 0.1\%$ , 其它值不能采用, 1.1) .a 描述。

- 2、应用中, 建议 PCB 大面积接地。这样可以消除由于接地点的不同而可能存在的电位不同, 同时可以降低电路板产生的电容对电路的影响。

- 3、使用时, 切忌电路插反, 否则可能导致电路损坏。

- 4、每个电源引脚需要就近接 1 个  $0.1\mu F$  和  $33\mu F$  的电容。

- 5、差分模拟输入部分走线必须等长。

- 6、数字电源和模拟电源需要分开。

- 7、该电路所有引出端均设计有静电保护结构, 不过大能量电脉冲仍然可能损坏电路, 因此在测试、搬运、储藏过程中, 应注意静电防护。

## 产品外形图

TQFP-128

## 包装/订购信息

| 产品型号          | 温度范围       | 产品封装   | 运输及包装数量   |

|---------------|------------|--------|-----------|

| CBM94AD34-500 | -40°C-85°C | QFN-56 | Tray, 260 |

| CBM94AD34-370 | -40°C-85°C | QFN-56 | Tray, 260 |

## 修订日志

| 版本   | 修订日期      | 变更内容 | 变更原因 | 制作 | 审核  | 备注 |

|------|-----------|------|------|----|-----|----|

| V1.0 | 2025.5.20 | 初版生成 | 常规更新 | WW | LYL |    |