# CD94AD67

16 位、200 MSPS/250 MSPS 模数转换器 (ADC)

版本: Rev 1.0.0 日期: 2025-5-20

## 产品特性

- 分辨率: 16 位

- 电源电压 3.3V/1.8V

- 最大采样率 250MSPS

- SNR: 72dBFS(170 MHz @ 250 MSPS)

- SFDR: 89dBc(170 MHz @ 250 MSPS)

- 60 fs rms jitter

- 微分非线性 DNL=±0.5LSB (典型)

- 积分非线性 INL=±3.5LSB (典型)

- 差分模拟输入范围≤2.5VPP

- SPI 功能

- DDR LVDS 输出 (ANSI-644 兼容)

- 内置时钟占空比稳定且有时钟输出

- 封装形式 QFN72

- 兼容 AD9467-250

## 产品应用

- 通信

- 接收器

- 基站

- 光谱分析

- 宽带无线

- 雷达

- 红外成像

- 功放线性化

- 图像处理

## 产品描述

CD94AD67 是一种 16 位单片中频采样模数转换器 (ADC)。它针对宽带高性能和易用性进行了优化。该产品以 250 MSPS 的转换速率运行，专为需要高动态范围的无线接收器、仪器和测试设备而设计。ADC 需要 1.8 V 和 3.3 V 电源以及低电压差分输入时钟才能实现全性能操作。许多应用不需要外部参考或驱动组件。数据输出与 LVDS 兼容 (ANSI-644 兼容)，并包括减少短跟踪距离所需总电流的方法。

提供用于捕获输出上的数据的数据时钟输出 (DCO)，用于向新的输出位发送信号。禁用时，通过 SPI 支持的内部断电功能通常消耗不到 5 mW。可选功能允许用户实现各种可选的操作条件，包括输入范围、数据格式选择和输出数据测试模式。CD94AD67 采用的是通过 - 工业温度范围为 40°C 至 +85°C。

## 目录

|                 |        |

|-----------------|--------|

| 产品特性 .....      | - 1 -  |

| 产品应用 .....      | - 1 -  |

| 产品描述 .....      | - 1 -  |

| 功能框图 .....      | - 3 -  |

| 引脚配置与功能描述 ..... | - 4 -  |

| 绝对最大额定值 .....   | - 6 -  |

| 电气特性 .....      | - 6 -  |

| 典型特性 .....      | - 7 -  |

| 控制功能 .....      | - 11 - |

| 应用说明 .....      | - 12 - |

| 使用注意事项 .....    | - 15 - |

| 封装外形及尺寸 .....   | - 16 - |

| 包装/订购信息 .....   | - 16 - |

| 修订日志 .....      | - 17 - |

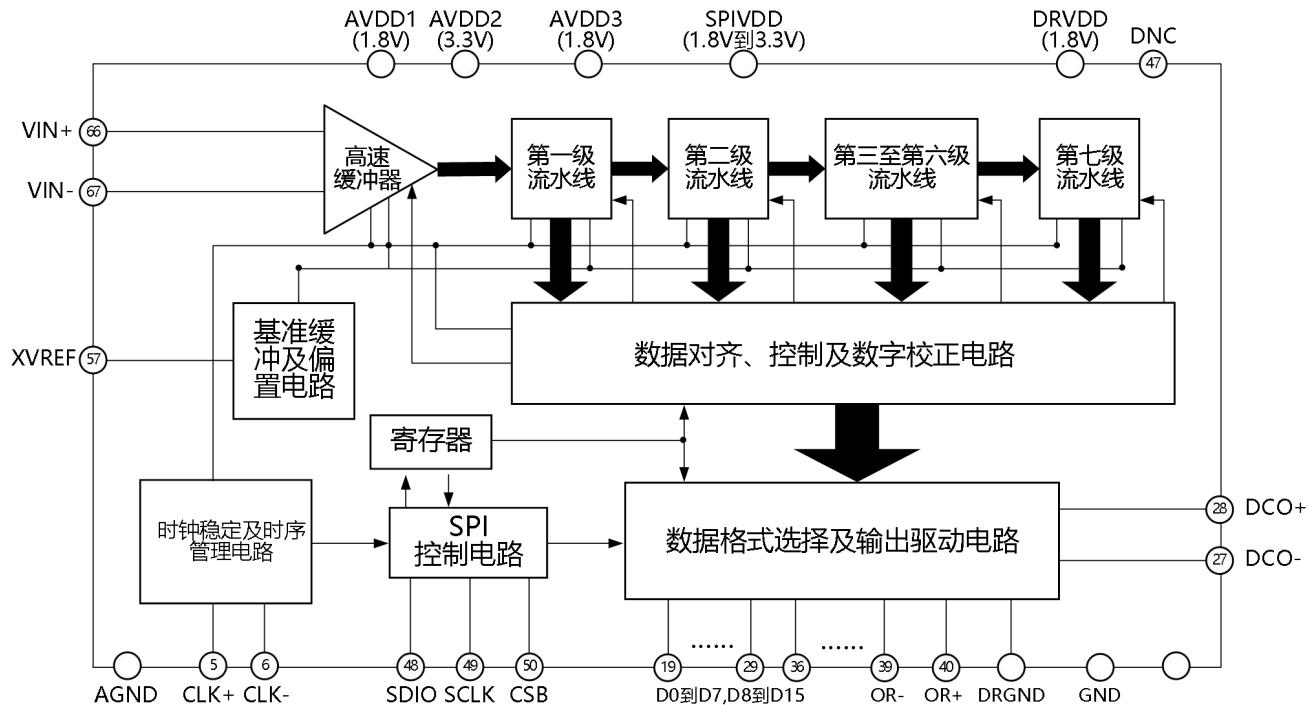

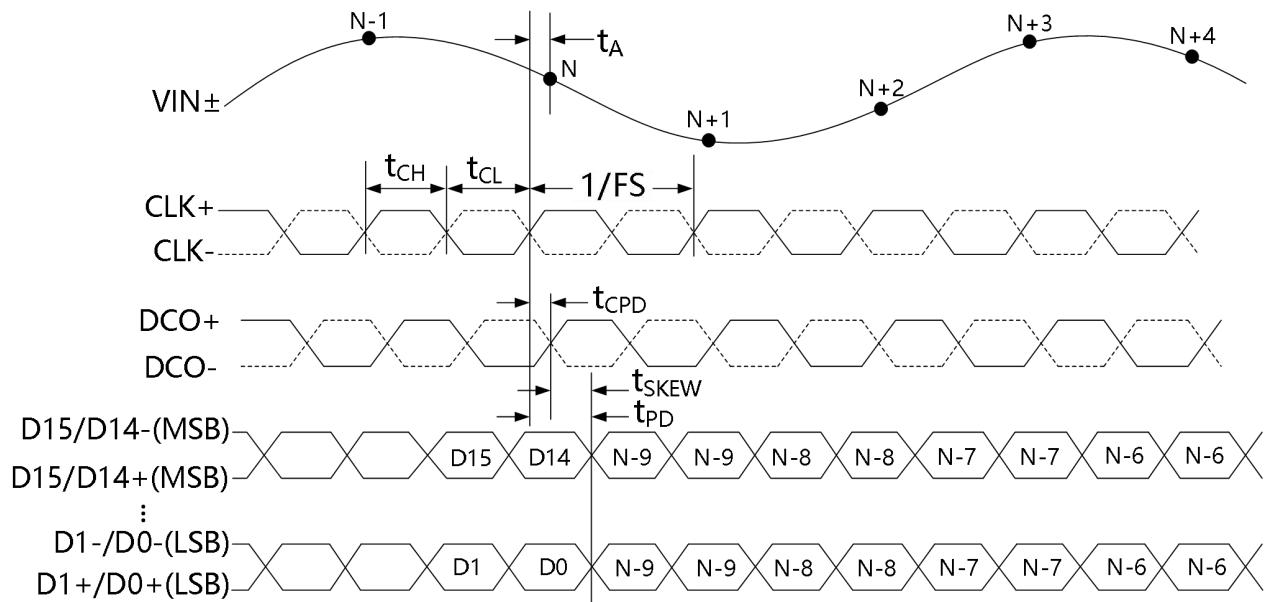

## 功能框图

该产品主要功能是将输入模拟信号转换为 16 位并行数字信号输出，主要用于采集高频宽带信号。电源电压 3.3V/1.8V，转换器包括前端缓冲器、流水线电路、逻辑校准、输出 IO、时钟处理电路、输出控制、基准等功能单元电路。该产品功能框图如图 1 所示，时序如图 2 所示。

图 1. 功能框图

图 2. 时序图

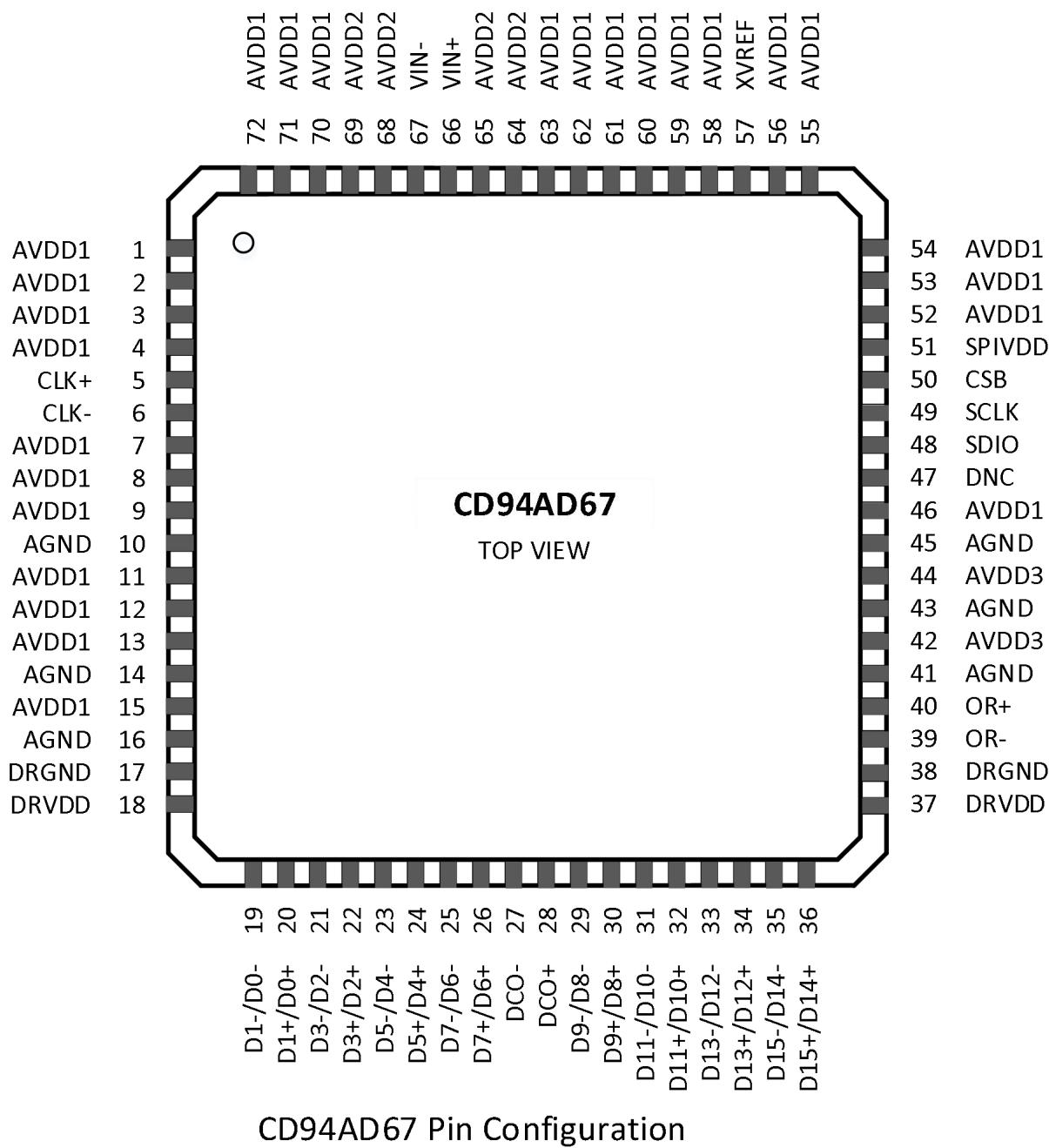

## 引脚配置与功能描述

### 引脚分配

## 引脚定义

表 1.引脚功能描述

| 管脚编号                                                                                            | 符号        | 功能                   |

|-------------------------------------------------------------------------------------------------|-----------|----------------------|

| 10,14,16,41,43,45                                                                               | AGND      | 模拟地                  |

| 1, 2, 3, 4, 7, 8, 9, 11, 12, 13, 15, 46, 52, 53, 54, 55, 56, 58, 59, 60, 61, 62, 63, 70, 71, 72 | AVDD1     | 1.8V模拟电源             |

| 64,65,68,69                                                                                     | AVDD2     | 3.3V模拟电源             |

| 42,44                                                                                           | AVDD3     | 1.8V模拟电源             |

| 51                                                                                              | SPIVDD    | 1.8 V或3.3 V SPI电源    |

| 17,38                                                                                           | DRGND     | 数字输出驱动地              |

| 18,37                                                                                           | DRVDD     | 1.8V数字输出驱动电源         |

| 67                                                                                              | VIN-      | 模拟输入负端               |

| 66                                                                                              | VIN+      | 模拟输入正端               |

| 6                                                                                               | CLK-      | 时钟输入负端               |

| 5                                                                                               | CLK+      | 时钟输入正端               |

| 19                                                                                              | D1-/D0-   | D1和D0数字输出负端          |

| 20                                                                                              | D1+/D0+   | D1和D0数字输出正端          |

| 21                                                                                              | D3-/D2-   | D3和D2数字输出负端          |

| 22                                                                                              | D3+/D2+   | D3和D2数字输出正端          |

| 23                                                                                              | D5-/D4-   | D5和D4数字输出负端          |

| 24                                                                                              | D5+/D4+   | D5和D4数字输出正端          |

| 25                                                                                              | D7-/D6-   | D7和D6数字输出负端          |

| 26                                                                                              | D7+/D6+   | D7和D6数字输出正端          |

| 29                                                                                              | D9-/D8-   | D9和D8数字输出负端          |

| 30                                                                                              | D9+/D8+   | D9和D8数字输出正端          |

| 31                                                                                              | D11-/D10- | D11和D10数字输出负端        |

| 32                                                                                              | D11+/D10+ | D11和D10数字输出正端        |

| 33                                                                                              | D13-/D12- | D13和D12数字输出输出负端      |

| 34                                                                                              | D13+/D12+ | D13和D12数字输出正端        |

| 35                                                                                              | D15-/D14- | D15 (MSB) 和D14数字输出负端 |

| 36                                                                                              | D15+/D14+ | D15 (MSB) 和D14数字输出正端 |

| 27                                                                                              | DCO-      | 数据时钟数字输出负端           |

| 28                                                                                              | DCO+      | 数据时钟数字输出正端           |

| 39                                                                                              | OR-       | 超出范围的数字输出负端          |

| 40                                                                                              | OR+       | 超出范围的数字输出正端          |

| 47                                                                                              | DNC       | 不连接 (引脚悬空)           |

| 48                                                                                              | SDIO      | 串行数据输入/输出            |

| 49                                                                                              | SCLK      | 串行时钟                 |

| 50                                                                                              | CSB       | 芯片选择栏                |

| 57                                                                                              | XVREF     | 外部VREF选项             |

## 绝对最大额定值

| 参数                          | 范围                   |

|-----------------------------|----------------------|

| AVDD 到 AGND                 | -0.3V 到 +2.0V        |

| DRVDD 到 DRGND               | -0.3V 到 +2.0V        |

| AGND 到 DRGND                | -0.3V 到 +0.3V        |

| AVDD 到 DRVDD                | -2.0V 到 +2.0V        |

| D0+/D0- 从 D11+/D11- 到 DRGND | -0.3V 到 DRVDD + 0.2V |

| DCO+, DCO- 到 DRGND          | -0.3V 到 DRVDD + 0.2V |

| OR+, OR- 到 DRGND            | -0.3V 到 DRVDD + 0.2V |

| CLK+ 到 AGND                 | -0.3V 到 AVDD + 0.2V  |

| CLK- 到 AGND                 | -0.3V 到 AVDD + 0.4V  |

| VIN+ 到 AGND                 | -0.3V 到 AVDD + 0.4V  |

| VIN- 到 AGND                 | -0.3V 到 AVDD + 0.2V  |

| CML 到 AGND                  | -0.3V 到 AVDD + 0.2V  |

| VREF 到 AGND                 | -0.3V 到 AVDD + 0.2V  |

| SDIO 到 DRGND                | -0.3V 到 DRVDD + 0.2V |

| PDWN 到 AGND                 | -0.3V 到 DRVDD + 0.2V |

| CSB 到 AGND                  | -0.3V 到 DRVDD + 0.2V |

| SCLK/DFS 到 AGND             | -0.3V 到 DRVDD + 0.2V |

| 工作温度                        | -40°C 到 +85°C        |

| 引脚温度 (焊接, 10s)              | 300°C                |

| 结温                          | 150°C                |

| 存储温度范围                      | -65°C 到 +125°C       |

## 电气特性

| 参数     | 符号       | 测试条件及说明        | CD94AD67-200 |           |     | CD94AD67-250 |           |     | 单位   |

|--------|----------|----------------|--------------|-----------|-----|--------------|-----------|-----|------|

|        |          |                | 最小值          | 典型值       | 最大值 | 最小值          | 典型值       | 最大值 |      |

| 分辨率    | --       | --             | 16           |           |     | 16           |           |     | Bits |

| 积分线性误差 | $E_L$    | $f_{IN}=10MHz$ | -16          | $\pm 3.5$ | 16  | -16          | $\pm 3.5$ | 16  | LSB  |

| 微分线性误差 | $E_{DL}$ | $f_{IN}=10MHz$ | -1           | $\pm 0.5$ | 1.5 | -1           | $\pm 0.5$ | 1.5 | LSB  |

| 失调电压误差 | $E_O$    | --             | -250         | -5        | 250 | -250         | -5        | 250 | LSB  |

|         |       |                                   |      |       |     |      |       |     |        |

|---------|-------|-----------------------------------|------|-------|-----|------|-------|-----|--------|

| 增益误差    | $E_G$ | --                                | -8   | -1.8  | 8   | -8   | -1.8  | 8   | %FSR   |

| 全功率带宽   | FPBW  | --                                | --   | 900   | --  | --   | 900   | --  | MHz    |

| 相位噪声抖动  | AUJ   | --                                | --   | 60    | --  | --   | 60    | --  | fs rms |

| 功耗      | $P_W$ | --                                | --   | --    | 1.8 | --   | 1.295 | 1.8 | W      |

| 信噪比     | SNR   | $f_{IN}=70MHz @ A_{IN}=-1$<br>dB  | 70   | 74.24 | --  | 70   | 74.42 | --  |        |

|         |       | $f_{IN}=140MHz @ A_{IN}=-1$<br>dB | 69   | 72.35 | --  | 69   | 72.75 | --  |        |

|         |       | $f_{IN}=170MHz @ A_{IN}=-1$<br>dB | 69   | 71.82 | --  | 69   | 72.03 | --  | dBFS   |

| 信噪失真比   | SINAD | $f_{IN}=70MHz @ A_{IN}=-1$<br>dB  | 70   | 74.20 | --  | 70   | 74.24 | --  |        |

|         |       | $f_{IN}=140MHz @ A_{IN}=-1$<br>dB | 69   | 72.52 | --  | 69   | 72.55 | --  | dBFS   |

|         |       | $f_{IN}=170MHz @ A_{IN}=-1$<br>dB | 69   | 71.84 | --  | 69   | 71.87 | --  |        |

| 有效位数    | ENOB  | $f_{IN}=70MHz @ A_{IN}=-1$<br>dB  | 11.2 | 12.00 | --  | 11.2 | 12.04 | --  |        |

|         |       | $f_{IN}=140MHz @ A_{IN}=-1$<br>dB | 11   | 11.75 | --  | 11   | 11.76 | --  | Bits   |

|         |       | $f_{IN}=170MHz @ A_{IN}=-1$<br>dB | 11   | 11.63 | --  | 11   | 11.65 | --  |        |

| 无杂散动态范围 | SFDR  | $f_{IN}=70MHz @ A_{IN}=-1$<br>dB  | 77   | 90.5  | --  | 77   | 91.31 | --  |        |

|         |       | $f_{IN}=140MHz @ A_{IN}=-1$<br>dB | 75   | 88    | --  | 75   | 89.04 | --  | dBFS   |

|         |       | $f_{IN}=170MHz @ A_{IN}=-1$<br>dB | 75   | 89    | --  | 75   | 89.05 | --  |        |

| 采样率     | SR    | --                                | 50   | --    | 200 | 50   | --    | 250 | MSPS   |

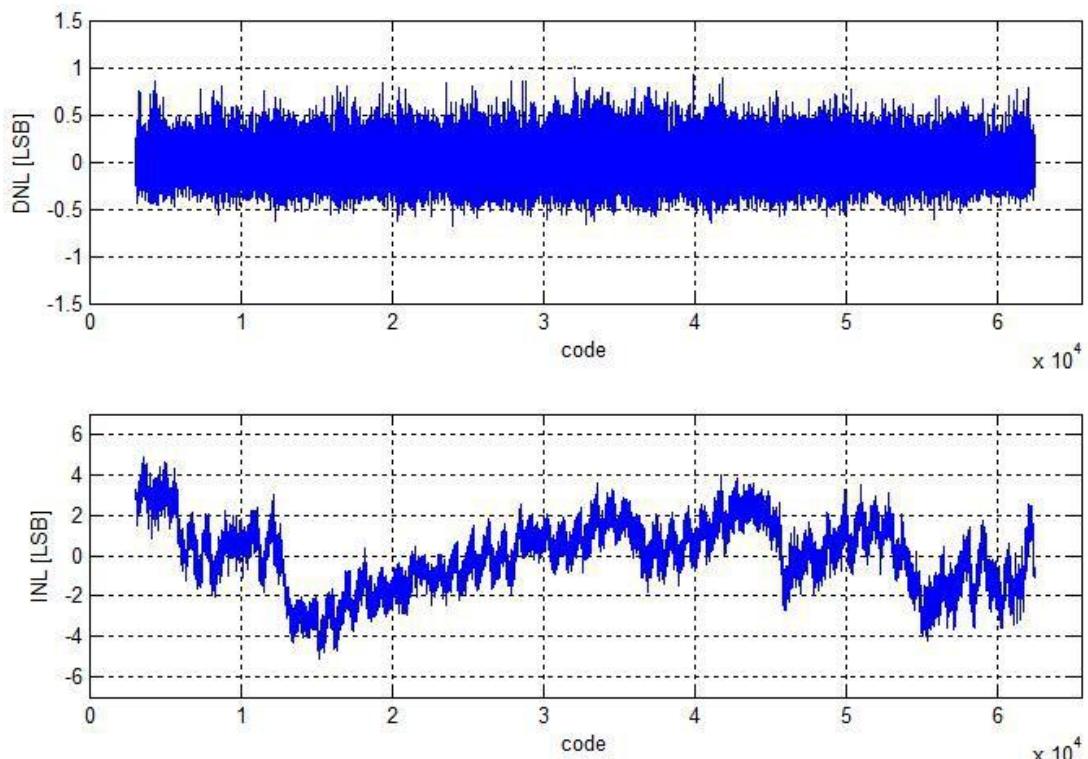

## 典型特性

INL 和 DNL 测试曲线如图 3 所示。

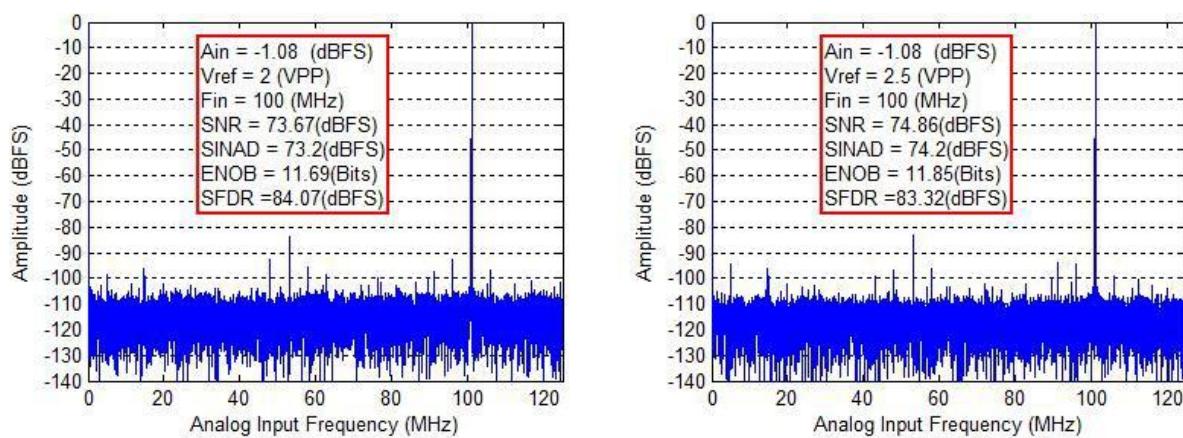

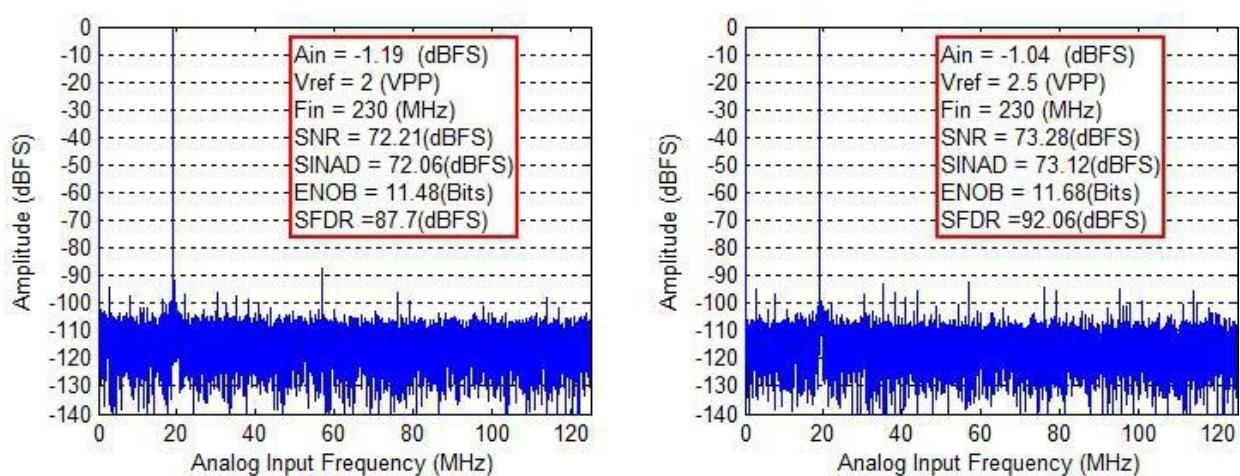

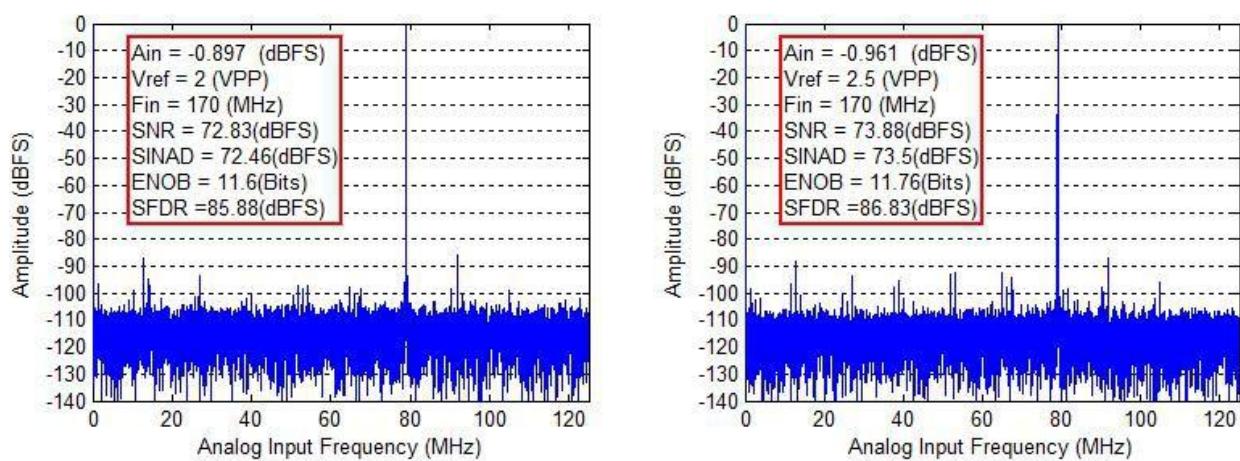

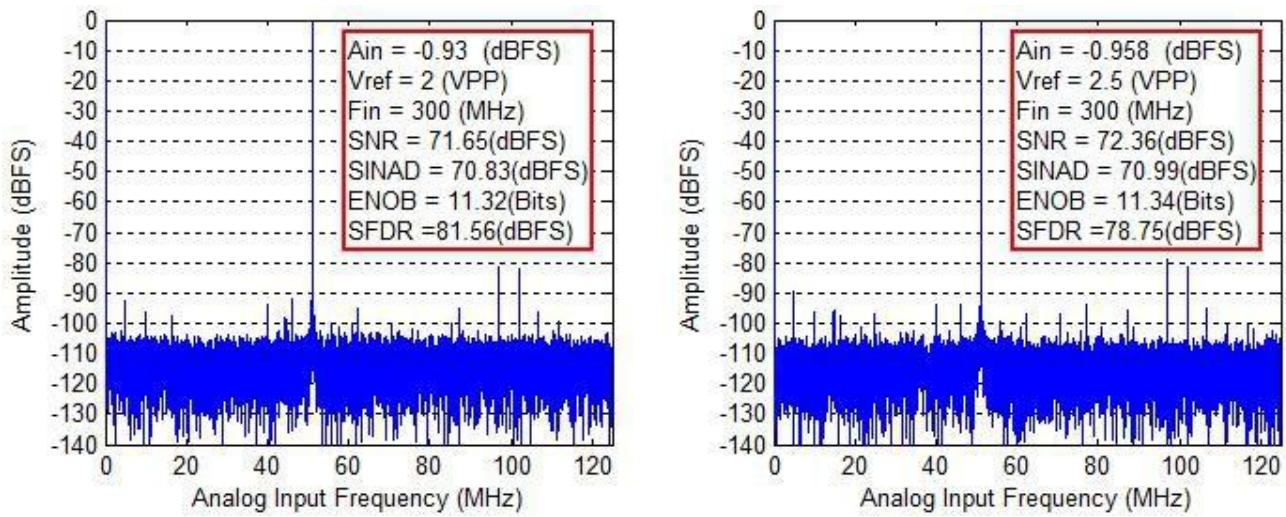

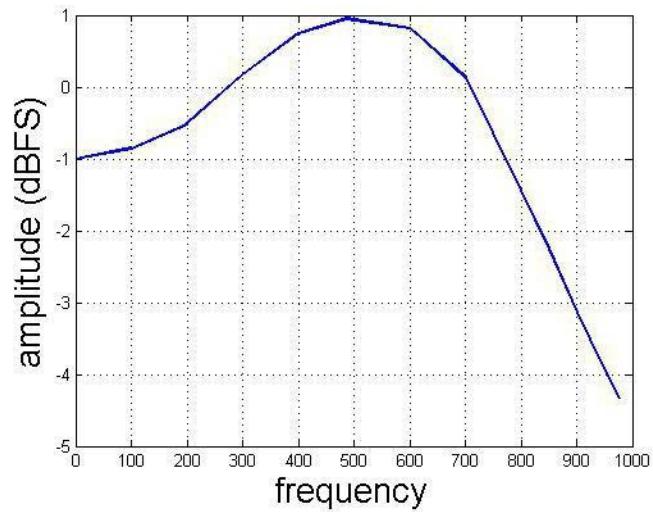

输入模拟输入频率 100MHz、采样率 250MSPS 的 FFT 如图 4 所示。输入模拟输入频率 170MHz、采样率 250MSPS 的 FFT 如图 5 所示。输入模拟输入频率 230MHz、采样率 250MSPS 的 FFT 如图 6 所示。输入模拟输入频率 300MHz、采样率 250MSPS 的 FFT 如图 7 所示。带宽测试如图 8 所示。

图 3. INL 和 DNL 典型测试图

图 4. FFT 特性：模拟输入频率 100MHz、采样率 250MSPS

图 7. FFT 特性: 模拟输入频率 300MHz、采样率 250MSPS

图 8. 全功率带宽特性

## 控制功能

| 地址 | 名称     | Bit7(M<br>SB)              | Bit<br>6 | Bit5                   | Bit4                        | Bit3    | Bit2                        | Bit1                                                                                                                                                                             | Bit<br>(LSB) | 默<br>认      | 备注                          |  |

|----|--------|----------------------------|----------|------------------------|-----------------------------|---------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-----------------------------|--|

| 08 | 模式     | X                          | X        | X                      | X                           | X       | X                           | 内部关断模式<br>00=工作(默认)<br>01=全芯片关断                                                                                                                                                  | 0X<br>00     | 决定芯片的一般工作模式 |                             |  |

| 09 | 时钟     | X                          | X        | X                      | X                           | X       | X                           | X                                                                                                                                                                                | 1=DCS        | 0X<br>01    |                             |  |

| 0C | 增强模式   | X                          | X        | X                      | X                           | X       | X                           | X                                                                                                                                                                                | 1=随机模式       | 0X<br>01    | 启用随机模式                      |  |

| 0D | 输出测试模式 | X                          | X        | 产生复位长PN序列(默认1=打开,0=关闭) | 产生复位短PN序列(默认1=打开,0=关闭)      | X       | X                           | 输出测试模式<br>0000=off(默认)<br>0001=midscale short<br>0010=+FS short<br>0011=-FS short<br>0100=checker-boardoutput<br>0101=PN23 sequence<br>0110=PN9 sequence<br>0111=1/0 word toggle |              | 0X<br>00    | 当取默认值之外的配置时, 测试模式数据取代正常数据输出 |  |

| 0E | BIST   | X                          | X        | X                      | X                           | X       | BIST启动                      | X                                                                                                                                                                                | BIST使能       | 0X<br>00    | BIST模式配置                    |  |

| 0F | ADC 输入 | XVREF<br>0=off(默认)<br>1=on |          |                        |                             |         | 模拟关断<br>0=off<br>默认<br>1=on |                                                                                                                                                                                  |              | 0X<br>00    | 模拟输入功能                      |  |

| 10 | Offset |                            |          |                        |                             |         |                             |                                                                                                                                                                                  |              | 0X<br>00    | Offset调整; 会结合01A0和01A1寄存器。  |  |

| 14 | 输出模式   | X                          | 0        | X                      | 输出关断<br>1=on<br>0=off<br>默认 | 1=DDR使能 | 输出反向<br>1=on<br>0=off默认     | 输出数据格式<br>00=偏移二进制(默认)<br>01=二进制补码<br>10=格雷码                                                                                                                                     |              | 0X<br>08    | 配置输出和数据格式                   |  |

| 15 | 输出调整   | X                          | X        | X                      | X                           | X       | 粗调<br>(0=3.0mA;1=1.71mA)    | 输出驱动电流调整: 001=3.0mA(默认)<br>010=2.79mA<br>011=2.57mA<br>100=2.35mA<br>101=2.14mA<br>110=1.93mA<br>111=1.71mA                                                                      |              | 0X<br>00    | 确定LVD或其他输出属性。               |  |

| 16 | 输出相位   | DCO输出反向<br>1=on<br>0=off   | X        | X                      | X                           | X       | X                           | X                                                                                                                                                                                | X            | 0X<br>00    | 决定数字输出时钟相位                  |  |

|         |             |                     |   |   |                               |   |                                |   |          |           |          |  |

|---------|-------------|---------------------|---|---|-------------------------------|---|--------------------------------|---|----------|-----------|----------|--|

| 17      | 输出延迟        | 使能<br>1=on<br>0=off | X | X | 延迟调整                          |   |                                |   | 0X<br>00 | 调整输出时钟的延迟 |          |  |

| 18      | Vref        | X                   | X | X | 输入满刻度范围调整                     |   |                                |   | 0X<br>0A | 调整Vref    |          |  |

|         |             |                     |   |   | 0000=2.0V <sub>p-p</sub>      |   |                                |   |          |           |          |  |

|         |             |                     |   |   | 0110=2.1V <sub>p-p</sub>      |   |                                |   |          |           |          |  |

|         |             |                     |   |   | 0111=2.2V <sub>p-p</sub>      |   |                                |   |          |           |          |  |

|         |             |                     |   |   | 1000=2.3V <sub>p-p</sub>      |   |                                |   |          |           |          |  |

|         |             |                     |   |   | 1001=2.4V <sub>p-p</sub>      |   |                                |   |          |           |          |  |

|         |             |                     |   |   | 1010=2.5V <sub>p-p</sub> (默认) |   |                                |   |          |           |          |  |

| 2C      | 模拟输入        | X                   | X | X | X                             | X | 输入耦合模式<br>默认:<br>0=ac,<br>1=dc | X | X        | 0X<br>00  | 决定输入耦合模式 |  |

| 36      | Buffer电流调整1 | 001000=+80%         |   |   |                               |   | 1                              | 0 | 0X<br>22 |           |          |  |

| 10<br>7 | Buffer电流调整2 | 001000=+80% (默认)    |   |   |                               |   | X                              | X | 0X<br>20 |           |          |  |

## 应用说明

### ● 输入信号

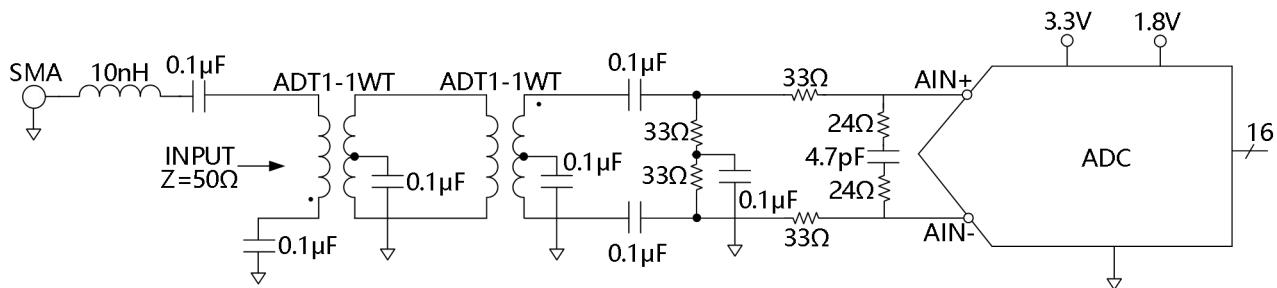

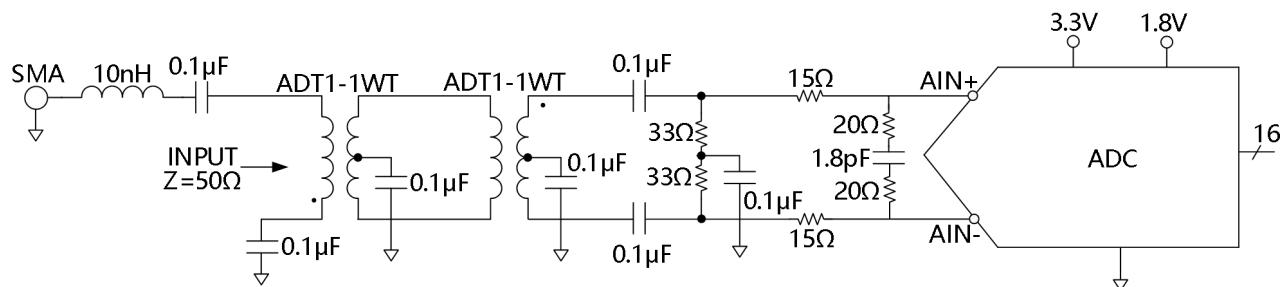

A/D 转换器模拟输入前端是一个差分缓冲器，为得到最好的动态性能，应匹配差分模拟端的源阻抗。输入端最好串联一个小电阻，有利于降低驱动源输出级的瞬态电流峰值。同时，在每个输入端上放置低 Q 值电感或者磁珠，使得模拟输入的差分电容减小，从而使 A/D 转换器带宽尽量高。高 IF 频率下，在驱动转换器的前端时，低 Q 值电感或者磁珠的使用非常必要。在输入放置一个并联电容或者两个单端电容，提供一个匹配的无源网络，最终在输入端产生一个低通滤波器，以滤掉带外噪声。推荐输入网络如图 9 和图 10 所示。

图 9. 低频输入前端网络 ( ~ 150MHz)

图 10. 高频输入前端网络 (中频输入 150MHz ~ 300MHz)

## ● 时序规格

### • 时钟输入结构及推荐端接方式

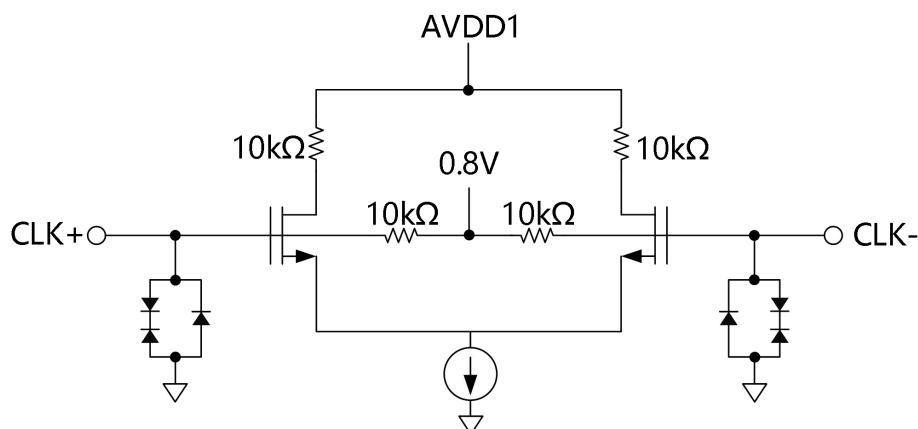

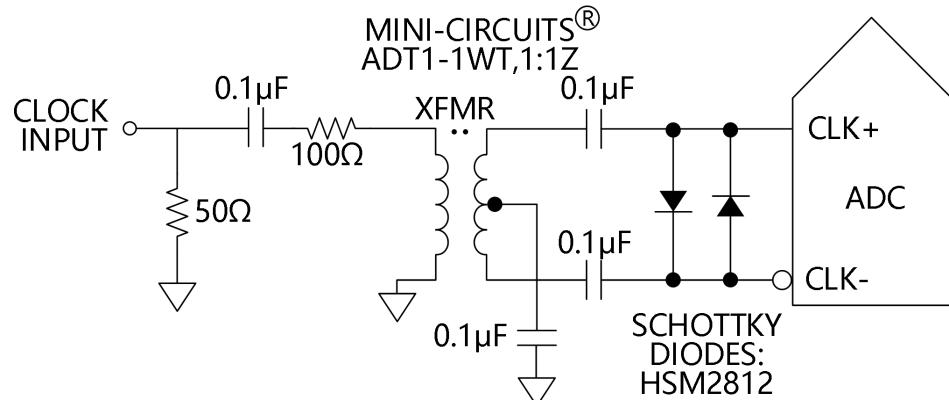

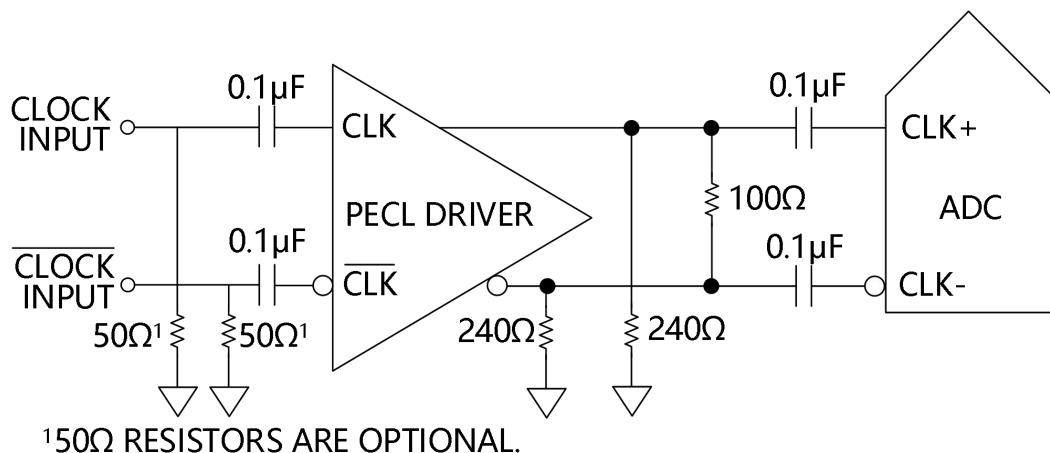

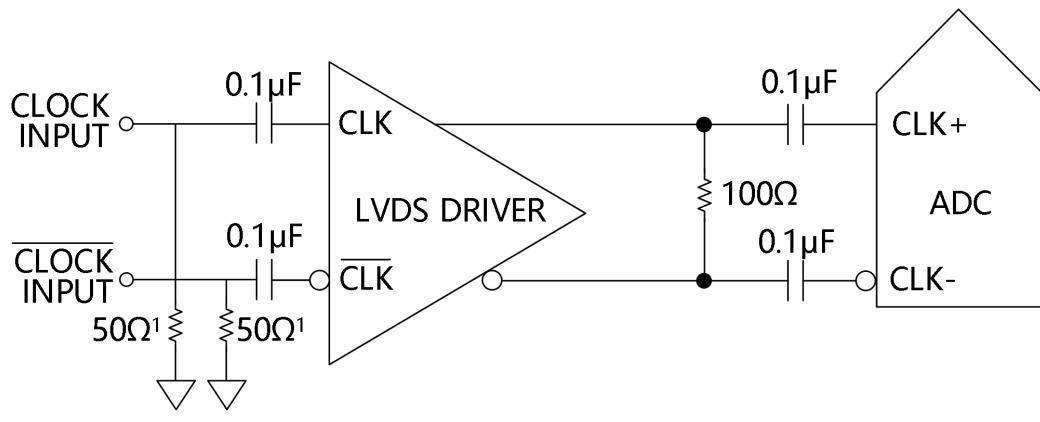

ADC 时钟输入结构如图 11 所示, 为差分输入结构, 内部提供 0.8V 共模电压。外部时钟应采用交流耦合方式激励。采用巴伦的推荐输入结构如图 12 所示。采用 LVPECL 驱动器的推荐输入结构如图 13 所示。如果采用 LVDS 驱动器, 推荐输入结构如图 14 所示。

图 11. ADC 时钟输入结构

图 12. 时钟巴伦激励方案

图 13. 时钟 LVPECL 信号激励方案

图 14-5 特发性跛行症治疗示意图

附錄六 考古

差分输入时钟信号幅度最小值为 250mVpp，兼容 LVDS/LVPECL 电平，时钟单端最大可允许幅度为  $V_{CM} \pm 0.9V$ 。为了减少时钟抖动并达到最优性能，应尽量提供上升和下降较快的时钟。正弦波输入情况下提高信号幅度可达到上述效果。在高频输入下，建议尽量增大时钟输入幅度。

上空比

ADC 内部电路采用输入时钟的双沿来产生各种时序信号, 为保证芯片发挥其优良性能, 应保证输入时钟占空比为  $(50 \pm 5)\%$ 。

## • 抖动

高速高精度 ADC 对时钟抖动十分敏感，尤其当输入信号频率较高时。信噪比 SNR 与抖动的关系为  $SNR = 20 \times \lg(1/(2\pi \times fIN \times tJitter))$ 。为保证本器件在高频模拟输入条件下具有最佳的 SNR，要求系统时钟抖动小于 100fs。

## • 推荐时钟设计方案

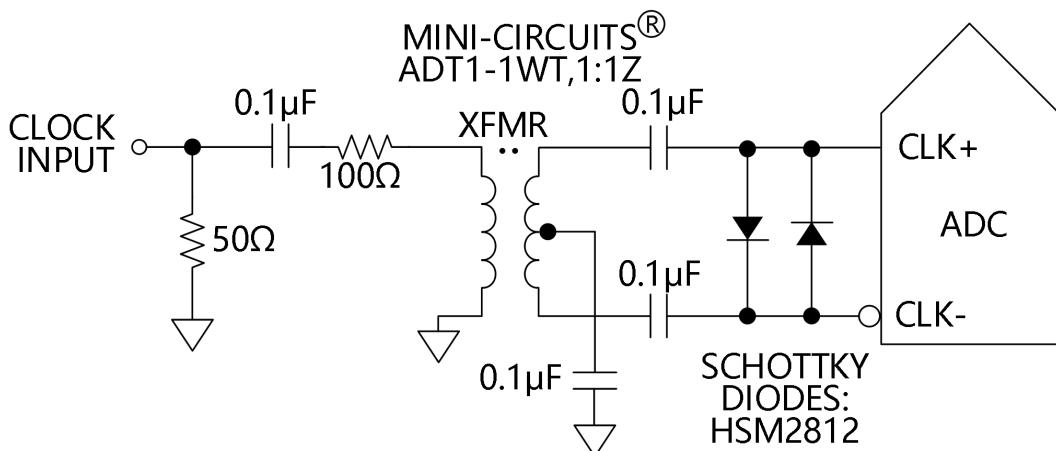

时钟方案采用单端转差分输入，变压器推荐使用 ADT1-1WT，输入输出分别用  $0.1\mu\text{F}$  陶瓷电容 AC 耦合。为获得对称波形，ADC 前可跨接两个背靠背的肖特基二极管。PCB 布线时，差分时钟走线要等长对称，且远离模拟输入端口，时钟与模拟输入端口之间做一些屏蔽（地覆铜）。推荐时钟设计方案如图 15

所示。

图 15. 推荐时钟方案

## 使用注意事项

- 1、热沉焊盘要与大地充分接触，应该通过尽量多的渠道和足够多的面积与 PCB 板的地层相连。

- 2、应用电路板有一个完整干净的地。

- 3、应用对象为多层布线板且内含独立的地层。

- 4、应用对象电路板的数字地和模拟地尽量分离，不要将数字线布于模拟线旁边或布于 A/D 转换器下。

- 5、模拟电源和数字输出电源端口要接高质量的陶瓷旁路电容，且旁路电容要尽量靠近管脚，连接管脚和旁路电容的连线越短越宽越好。

- 6、差分输入应尽量靠近且相互平行。

- 7、输入连线应尽量短以最小化寄生电容和噪声引入。

- 8、产品所有引出端均设计有静电保护结构，不过大能量电脉冲仍然可能损坏电路，因此在测试、搬运、储藏过程中，应注意静电防护。

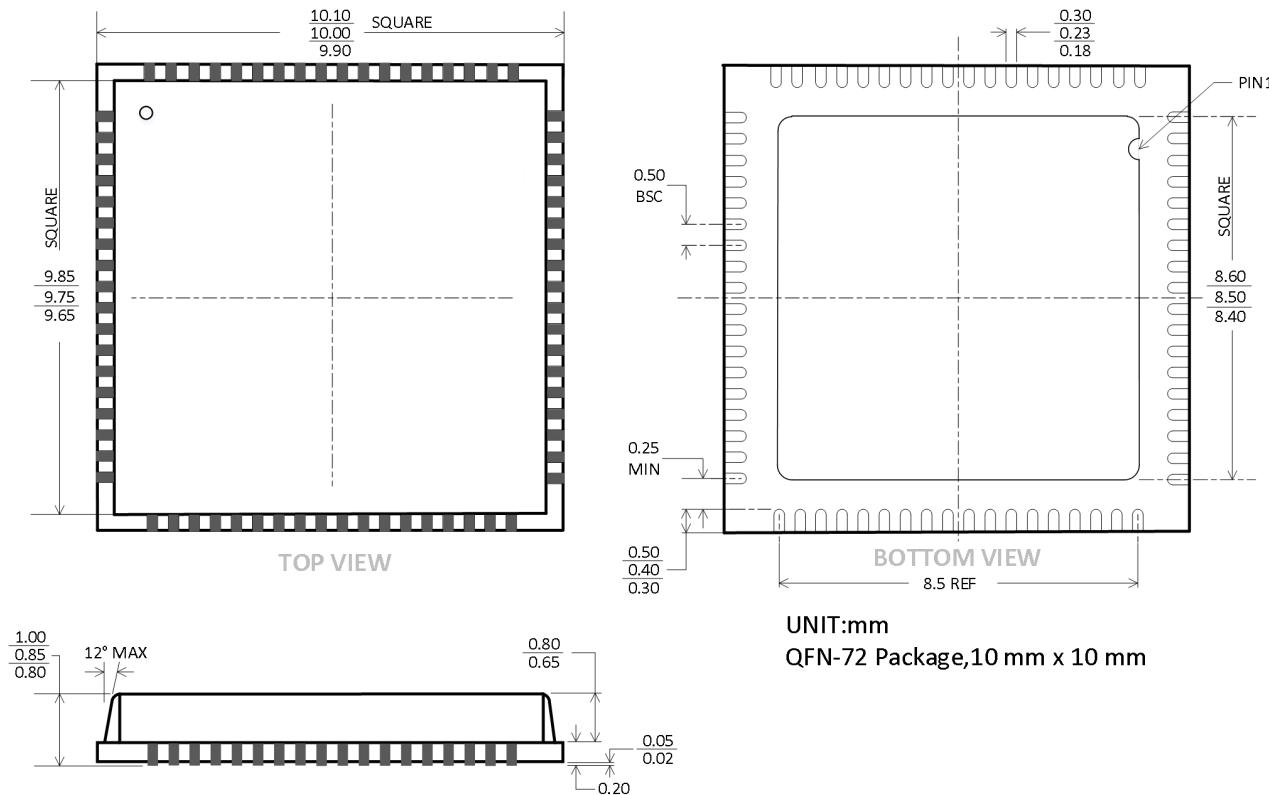

## 封装外形及尺寸

### QFN-72

## 包装/订购信息

| 产品型号         | 温度范围       | 产品封装   | 运输及包装数量   |

|--------------|------------|--------|-----------|

| CD94AD67-200 | -40°C+85°C | QFN-72 | Tray, 168 |

| CD94AD67-250 | -40°C+85°C | QFN-72 | Tray, 168 |

## 修订日志

| 版本   | 修订日期      | 变更内容 | 变更原因 | 制作 | 审核  | 备注 |

|------|-----------|------|------|----|-----|----|

| V1.0 | 2025.5.20 | 初版生成 | 常规更新 | WW | LYL |    |