# CD53D04\_CD53D14\_CD53D24

2.5 V 至 5.5 V、500  $\mu$ A、4 通道、电压输出、8/10/12 位 DAC

版本: Rev 1.0.0 日期: 2025-7-1

## 产品特性

- CD53D04:四路缓冲电压输出, 8 位数模转换器 (DACs) , 10 引脚 MSOP, 10 引脚 QFN 封装

- CD53D14:四路缓冲电压输出, 10 位数模转换器 (DACs) , 10 引脚 MSOP, 10 引脚 QFN 封装

- CD53D24:四路缓冲电压输出, 12 位数模转换器 (DACs) , 10 引脚 MSOP, 10 引脚 QFN 封装

- 低功率运行: 500uA @ 3V,600uA @ 5V

- 供电电源电压: 2.5V 至 5.5V

- 休眠模式下: 80nA @ 3V, 200nA @ 5V

- 双缓冲输入逻辑

- 输出电压范围: 0V 至 VREF (基准电压值)

- 上电复位电压归零 (0V)

- 集成芯片, 轨至轨输出缓冲放大器

- 温度范围: -40°C 至 +105°C

## 产品应用

- 便携式电池供电仪器

- 数字增益和偏移调整

- 可编程电压源和电流源

- 可编程衰减器

- 工业过程控制

## 产品描述

CD53D04/CD53D14/CD53D24 是 4 路缓冲电压输出, 8/10/12 位数模转换器 (DACs) , 采用 10 引脚封装, 单电源供电, 供电电压范围为 2.5V 至 5.5V, 3V 下消耗电流只有 500uA。这些转换器是集成芯片、轨至轨输出放大器, 电压转换速率为 0.7V/us, 3 线串行接口兼容 SPI, QSPI, MICROWIRE, DSP 接口标准, 能够工作在最大 30MHz 的时钟频率下。

4 路数模转换器 (DACs) 基准电压来源于一个参考引脚, 所有的数模转换器 (DACs) 输出电压同步更新。它包含一个启动复位电路, 该电路确保电源电压上升至有效电压时, 数模转换器 (DAC) 输出电压为 0V, 并一直保持该状态直到接收到新的状态更新命令。休眠模式的特点可以降低电流消耗至 200nA@5V (80nA @ 3V)。

## 目录

|                 |        |

|-----------------|--------|

| 产品特性 .....      | - 1 -  |

| 产品应用 .....      | - 1 -  |

| 产品描述 .....      | - 1 -  |

| 功能框图 .....      | - 3 -  |

| 典型应用电路 .....    | - 3 -  |

| 绝对最大额定值 .....   | - 4 -  |

| 推荐工作范围 .....    | - 4 -  |

| 电气特性 .....      | - 4 -  |

| 引脚配置与功能描述 ..... | - 8 -  |

| 典型性能 .....      | - 9 -  |

| 封装外形及尺寸 .....   | - 15 - |

| 包装/订购信息 .....   | - 17 - |

| 修订日志 .....      | - 18 - |

## 功能框图

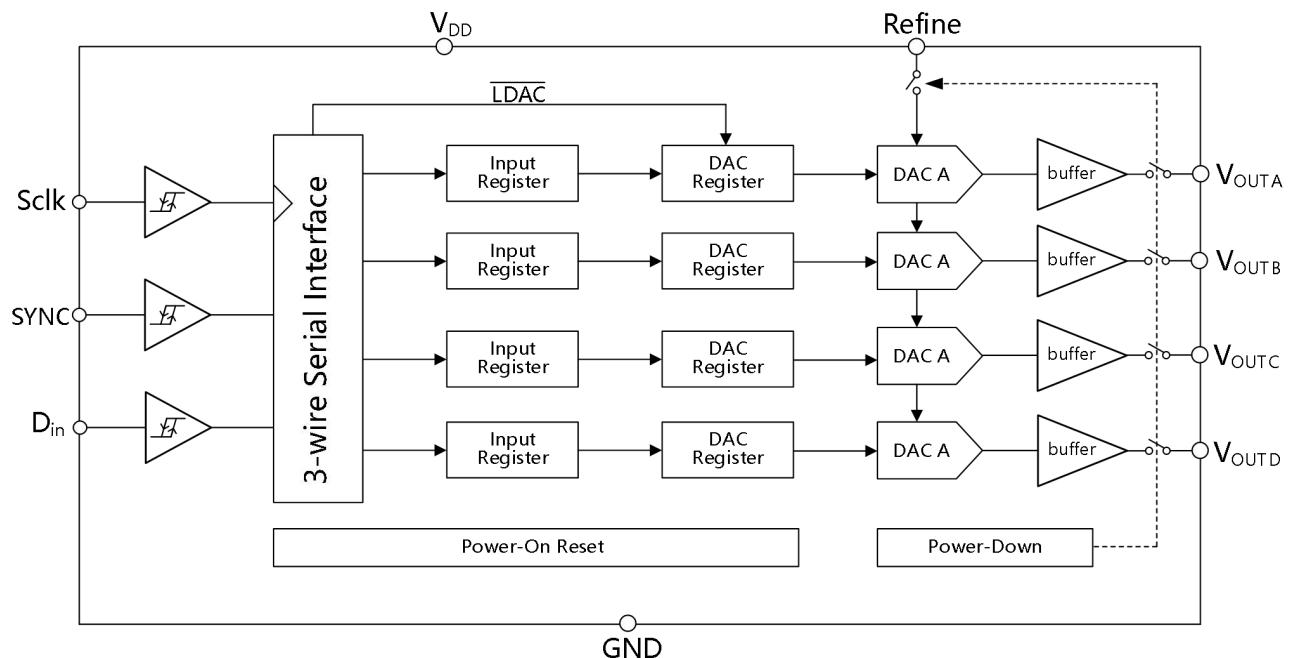

图 1. 功能框图

## 典型应用电路

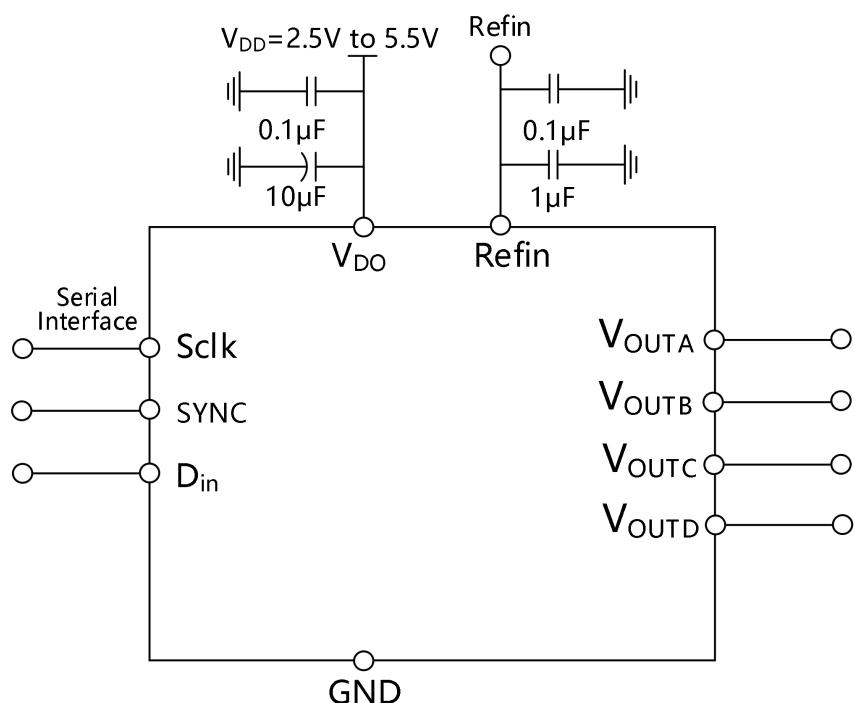

图 2. CD53D04/CD53D14/CD53D24 典型应用电路

## 绝对最大额定值

( $T_A=25^\circ\text{C}$ , 特殊说明除外。)

| 参数 <sup>1</sup> | 符号           | 数值                     |

|-----------------|--------------|------------------------|

| 电源电压相对地         | $V_{DDabs}$  | -0.3V to +7V           |

| 数字输入电压相对地       | $V_{Digabs}$ | -0.3V to $V_{DD}+0.3V$ |

| 参考输入电压相对地       | $V_{refabs}$ | -0.3V to $V_{DD}+0.3V$ |

| A ~ D 相对地       | $V_{outabs}$ | -0.3V to $V_{DD}+0.3V$ |

| 工作温度范围   |            |                 |

|----------|------------|-----------------|

| 工业应用温度范围 | $T_P$      | -40°C to +105°C |

| 存储温度范围   | $T_S$      | -65°C to +150°C |

| 最大结温     | $T_{Jmax}$ | 150°C           |

| 回流焊接              |  |                  |

|-------------------|--|------------------|

| 峰值温度(Pb-free)     |  | 260°C            |

| 峰值温度(non Pb-free) |  | 220°C            |

| 峰值温度时间            |  | 10 sec to 40 sec |

## 推荐工作范围

| 参数   | 符号       | 范围   |      | 单位 |

|------|----------|------|------|----|

|      |          | 最小值  | 最大值  |    |

| 电源电压 | $V_{DD}$ | 2.5  | 5.5  | V  |

| 耗散电流 | $I_{DD}$ | 400u | 600u | A  |

| 环境温度 | $T_a$    | -40  | 105  | °C |

## 电气特性

( $V_{DD}=2.5\text{V}$  至  $5.5\text{V}$ ;  $V_{REF}=2\text{V}$ ;  $R_L=2\text{K}\Omega$  到地 (GND) ;  $C_L=200\text{pF}$  到地 (GND) ;  $T_a=25^\circ\text{C}$ ; 除非另外说明。)

| 参数                   | 符号             | 测试条件  | A 版本 |     |     | B 版本 |     |     | 单位   |  |  |  |

|----------------------|----------------|-------|------|-----|-----|------|-----|-----|------|--|--|--|

|                      |                |       | 最小值  | 典型值 | 最大值 | 最小值  | 典型值 | 最大值 |      |  |  |  |

| <b>直流 (DC) 性能1,2</b> |                |       |      |     |     |      |     |     |      |  |  |  |

| CD53D04              |                |       |      |     |     |      |     |     |      |  |  |  |

| 分辨率                  | $\text{Res}_N$ | 确保单调性 | 8    |     |     | 8    |     |     | Bits |  |  |  |

|       |     |  |  |       |       |  |       |        |     |

|-------|-----|--|--|-------|-------|--|-------|--------|-----|

| 积分非线性 | INL |  |  | ±0.15 | ±1.15 |  | ±0.15 | ±0.625 | LSB |

| 差分非线性 | DNL |  |  | ±0.02 | ±0.25 |  | ±0.02 | ±0.25  | LSB |

#### CD53D14

|       |                  |       |    |       |       |    |       |      |     |

|-------|------------------|-------|----|-------|-------|----|-------|------|-----|

| 分辨率   | Res <sub>N</sub> | 确保单调性 | 10 |       |       | 10 |       | Bits |     |

| 积分非线性 | INL              |       |    | ±0.5  | ±4.05 |    | ±0.5  | ±2.5 | LSB |

| 差分非线性 | DNL              |       |    | ±0.05 | ±0.5  |    | ±0.05 | ±0.5 | LSB |

#### CD53D24

|                        |                  |                                       |    |       |        |    |       |      |          |

|------------------------|------------------|---------------------------------------|----|-------|--------|----|-------|------|----------|

| 分辨率                    | Res <sub>N</sub> | 确保单调性                                 | 12 |       |        | 12 |       | Bits |          |

| 积分非线性                  | INL              |                                       |    | ±2    | ±16.05 |    | ±2    | ±10  | LSB      |

| 差分非线性                  | DNL              |                                       |    | ±0.2  | ±1     |    | ±0.2  | ±1   | LSB      |

| 偏移误差                   |                  |                                       |    | ±0.4  | ±3     |    | ±0.4  | ±3   | % of FSR |

| 增益误差                   |                  |                                       |    | ±0.15 | ±1     |    | ±0.15 | ±1   | % of FSR |

| 低电平死区                  |                  | 低死区仅在偏移误差为负时存在                        |    |       |        |    | 20    |      | mV       |

| 直流电源共模抑制比 <sup>3</sup> | PSR R            | $\Delta V_{DD} = \pm 10\%$            |    | -60   |        |    | -60   |      | dB       |

| 直流干扰 <sup>3</sup>      |                  | $R_L = 2K\Omega$ 到地 (GND) or $V_{DD}$ |    | 200   |        |    | 200   |      | uV       |

#### 参考输入<sup>3</sup>

|          |  |          |      |     |          |      |     |          |           |

|----------|--|----------|------|-----|----------|------|-----|----------|-----------|

| 基准输入电压范围 |  |          | 0.25 |     | $V_{DD}$ | 0.25 |     | $V_{DD}$ | V         |

| 基准输入阻抗   |  |          | 37   | 45  |          | 37   | 45  |          | $K\Omega$ |

| 基准馈入     |  | 频率=10KHz |      | -90 |          |      | -90 |          | dB        |

#### 输出特性<sup>3</sup>

|                     |  |               |  |                  |  |  |                  |  |          |

|---------------------|--|---------------|--|------------------|--|--|------------------|--|----------|

| 最小输出电压 <sup>4</sup> |  |               |  | 0.001            |  |  | 0.001            |  | V        |

| 最大输出电压 <sup>4</sup> |  |               |  | $V_{DD} - 0.001$ |  |  | $V_{DD} - 0.001$ |  | V        |

| 直流输出阻抗              |  |               |  | 0.5              |  |  | 0.5              |  | $\Omega$ |

| 短路电流                |  | $V_{DD} = 5V$ |  | 25               |  |  | 25               |  | mA       |

|                     |  | $V_{DD} = 3V$ |  | 16               |  |  | 16               |  | mA       |

|      |  |                |     |  |  |     |  |    |

|------|--|----------------|-----|--|--|-----|--|----|

| 启动时间 |  | 退出断电模式 VDD=5 V | 5   |  |  | 5   |  | μs |

|      |  | 退出断电模式 VDD=3 V | 2.5 |  |  | 2.5 |  | μs |

### 逻辑输入<sup>3</sup>

|       |                 |                   |     |     |     |     |  |    |

|-------|-----------------|-------------------|-----|-----|-----|-----|--|----|

| 低电压输入 | V <sub>IL</sub> | VDD = 5 V ± 10%   |     | 0.8 |     | 0.8 |  | V  |

|       |                 | VDD = 3 V ± 10%   |     | 0.6 |     | 0.6 |  | V  |

|       |                 | VDD = 2.5 V ± 10% |     | 0.5 |     | 0.5 |  | V  |

| 高电压输入 | V <sub>IH</sub> | VDD = 5 V ± 10%   | 2.4 |     | 2.4 |     |  | V  |

|       |                 | VDD = 3 V ± 10%   | 2.1 |     | 2.1 |     |  | V  |

|       |                 | VDD = 2.5 V ± 10% | 2.0 |     | 2.0 |     |  | V  |

| 电容    |                 |                   | 3   |     |     | 3   |  | pF |

### 电源要求

|        |                 |  |  |  |     |  |     |  |   |

|--------|-----------------|--|--|--|-----|--|-----|--|---|

| 供电电源电压 | V <sub>DD</sub> |  |  |  | 2.5 |  | 5.5 |  | V |

|--------|-----------------|--|--|--|-----|--|-----|--|---|

### I<sub>DD</sub> (标准模式)<sup>4</sup>

|                                 |  |                                                         |  |     |     |  |     |     |    |

|---------------------------------|--|---------------------------------------------------------|--|-----|-----|--|-----|-----|----|

| V <sub>DD</sub> =4.5V<br>至 5.5V |  | V <sub>IH</sub> =V <sub>DD</sub> 和 V <sub>IL</sub> =GND |  | 600 | 900 |  | 600 | 900 | uA |

| V <sub>DD</sub> =2.5V<br>至 3.6V |  | V <sub>IH</sub> =V <sub>DD</sub> 和 V <sub>IL</sub> =GND |  | 500 | 700 |  | 500 | 700 | uA |

### I<sub>DD</sub> (休眠模式)

|                                 |  |                                                         |  |      |   |  |      |   |    |

|---------------------------------|--|---------------------------------------------------------|--|------|---|--|------|---|----|

| V <sub>DD</sub> =4.5V<br>至 5.5V |  | V <sub>IH</sub> =V <sub>DD</sub> 和 V <sub>IL</sub> =GND |  | 0.2  | 1 |  | 0.2  | 1 | uA |

| V <sub>DD</sub> =2.5V<br>至 3.6V |  | V <sub>IH</sub> =V <sub>DD</sub> 和 V <sub>IL</sub> =GND |  | 0.08 | 1 |  | 0.08 | 1 | uA |

1. 不加载输出的直流 (DC) 规格测试。

2. 线性特性测试时, 输入码范围: CD53D04 (Code 8 to Code 248), CD53D14 (Code 28 to Code 995), CD53D24 (Code 115 to Code 3981)。

3. 设计值非实际测试值。

4. 如果放大器输出达到最小电压值, 偏移误差必须为负。如果放大器输出达到最大电压值, VREF=VDD 和偏移与增益误差必须为正。

5. 标准模式 (IDD) 下, 其规格对所有数模转换 (DAC) 、所有数模转换器 (DACs) 输入码有效, 不包括负载电流, 对接口无效。

### 交流特性

(V<sub>DD</sub>=2.5V 至 5.5V; V<sub>REF</sub>=2V; R<sub>L</sub>=2KΩ 到地 (GND) ; C<sub>L</sub>=200pF 到地 (GND) ; Ta=25°C; 除非另外说明。)

| 参数 1 | 符号 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|------|----|------|-----|-----|-----|----|

|------|----|------|-----|-----|-----|----|

### 输出电压设定时间

|              |                                           |     |  |        |

|--------------|-------------------------------------------|-----|--|--------|

| CD53D04      | 1/4 范围 to 3/4 范围变化<br>(0x40 到 0xC0)       | 7   |  | uS     |

| CD53D14      | 1/4 范围 to 3/4 范围变化<br>(0x100 到 0x300)     | 8   |  | uS     |

| CD53D24      | 1/4 范围 to 3/4 范围变化<br>(0x400 到 0xC00)     | 9   |  | uS     |

| 压摆率          |                                           | 0.7 |  | V/uS   |

| 主要代码转换毛刺能量   | 1 LSB 改变进位                                | 40  |  | nV-sec |

| 数字馈通         |                                           | 1   |  | nV-sec |

| 数字串扰         |                                           | 1   |  | nV-sec |

| DAC-到-DAC 串扰 |                                           | 3   |  | nV-sec |

| 最大带宽         | $V_{REF}=2V \pm 0.1V_{P-P}$               | 200 |  | kHz    |

| 总谐波失真        | $V_{REF}=2.5V \pm 0.1V_{P-P}$<br>频率=10KHz | -70 |  | dB     |

1. 设计值非实际测试值。

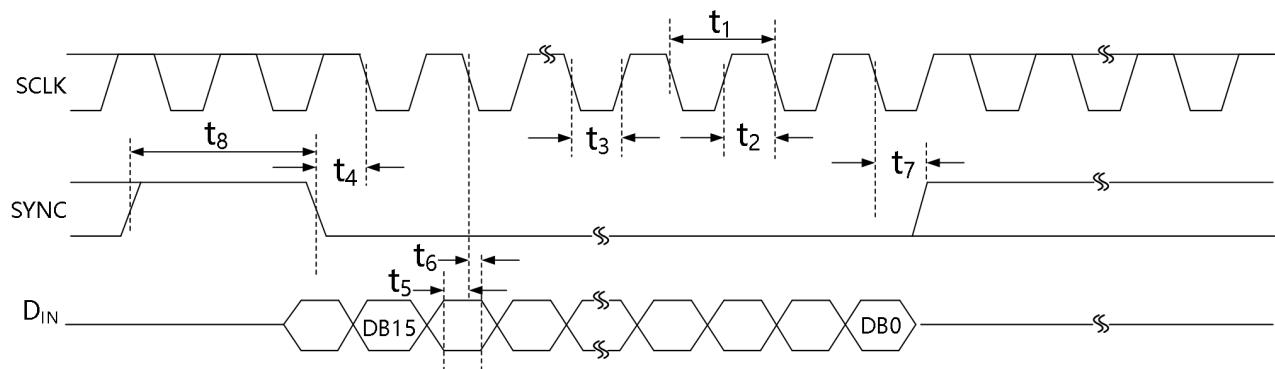

### 时序特性

$V_{DD} = 2.5V$  至  $5.5V$ ; 对所有转换器  $T_{MIN}$  至  $T_{MAX}$ , 除非另外说明。

| 参数 1, 2, 3 | TMIN, TMAX 极值   |                 | 单位     | 测试条件/备注            |

|------------|-----------------|-----------------|--------|--------------------|

|            | VDD=2.5V 至 3.6V | VDD=3.6V 至 5.5V |        |                    |

| $t_1$      | 40              | 33              | ns min | SCLK 循环时间          |

| $t_2$      | 16              | 13              | ns min | SCLK 高电平时间         |

| $t_3$      | 16              | 13              | ns min | SCLK 低电平时间         |

| $t_4$      | 16              | 13              | ns min | SYNC至SCLK 下降沿设置时间  |

| $t_5$      | 5               | 5               | ns min | 数据设置时间             |

| $t_6$      | 4.5             | 4.5             | ns min | 数据保持时间             |

| $t_7$      | 0               | 0               | ns min | SCLK 下降沿到SYNC上升沿时间 |

| $t_8$      | 80              | 33              | ns min | 最小SYNC高电平时间        |

1. 设计值非实际测试值。

2. 所有输入信号指定为  $tr = tf = 5ns$  ( $V_{DD}$  的 10% 至 90%), 信号时间从  $(V_{IL} + V_{IH})/2$  开始。

3. 如图 3。

图 3. 串联接口时序图

## 引脚配置与功能描述

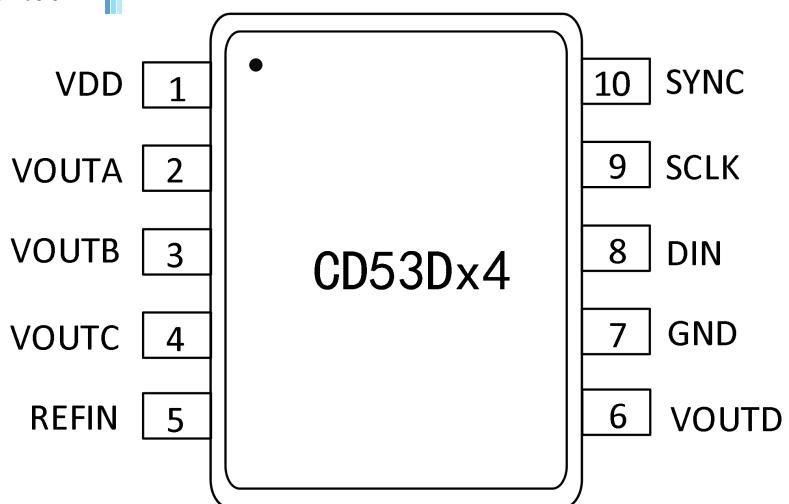

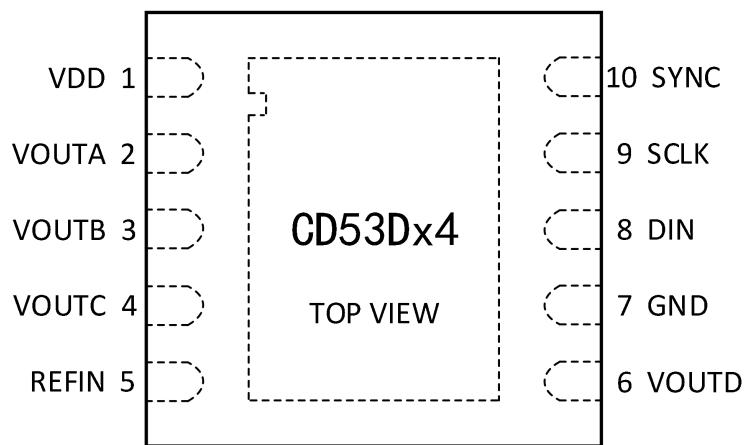

图 4.10 引脚 MSOP 引脚配置

图 5.10 引脚 QFN 引脚配置

### 引脚功能描述

| 引脚名称  | 序号 | 引脚功能   | 引脚描述                                                                                                                                        |

|-------|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| VDD   | 1  | Power  | 电源输入。电源输入范围为 2.7V~5.5V, 工作时接去耦合电容到地。                                                                                                        |

| VOUTA | 2  | O      | A通道缓冲模拟输出电压, 输出放大器轨至轨工作。                                                                                                                    |

| VOUTB | 3  | O      | B通道缓冲模拟输出电压, 输出放大器轨至轨工作。                                                                                                                    |

| VOUTC | 4  | O      | C通道缓冲模拟输出电压, 输出放大器轨至轨工作。                                                                                                                    |

| REFIN | 5  | I      | 所有的四路数模转换器 (DACs) 的基准输入引脚, 输入电压范围为0.25V到V <sub>DD</sub>                                                                                     |

| VOUTD | 6  | O      | D通道缓冲模拟输出电压, 输出放大器轨至轨工作。                                                                                                                    |

| GND   | 7  | Ground | 整个芯片的地电位参考电压                                                                                                                                |

| DIN   | 8  | I      | 串行数据输入。<br>该设备有16位移位寄存器<br>在帧同步信号变高前, 串行时钟信号下降沿将数据输入至移位寄存器。Din引脚输入缓冲在每个写循环后休眠。                                                              |

| SCLK  | 9  | I      | 串行时钟输入。<br>在该时钟的下降沿, 数字信号被输入至移位寄存器, 时钟最高工作频率为30MHz。Sclk Din引脚输入缓冲在每个写循环后休眠。                                                                 |

| SYNC  | 10 | I      | 有效低电平控制输入。<br>帧同步输入信号。当该信号为低时, 数字信号在时钟下降沿写入至输入移位寄存器。<br>时钟信号出现 16 个下降沿后, 该信号的上升沿使 DAC 输出更新。若该信号在 15 个上升沿前变高, 该信号的上升沿视为中断信号, DAC 的输出将忽略输入序列。 |

I: 输入, O: 输出

### 典型性能

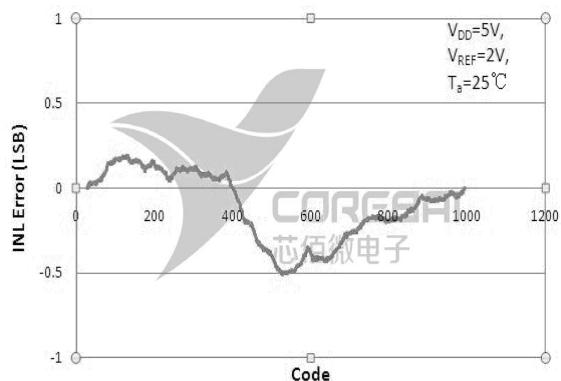

图 6. CD53D14 Typical INL Plot

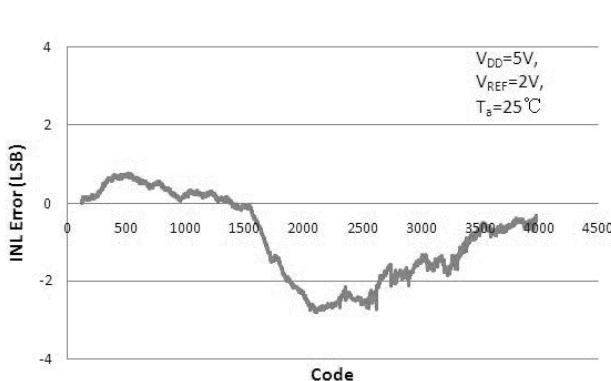

图 7. CD53D24 Typical INL Plot

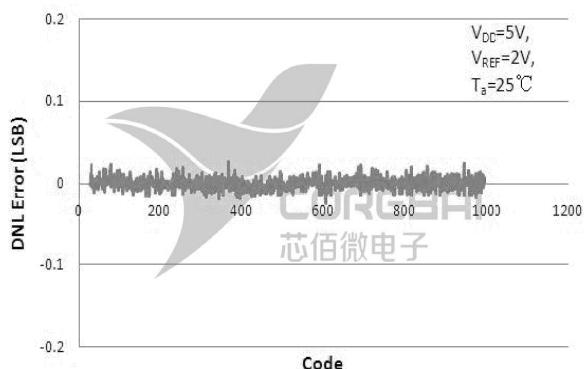

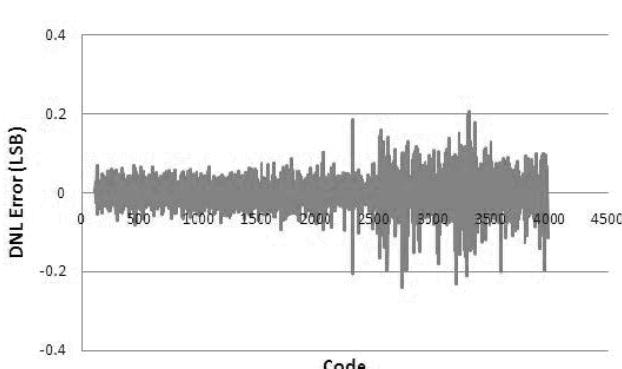

图 8. CD53D14 Typical DNL Plot

图 9. CD53D24 Typical DNL Plot

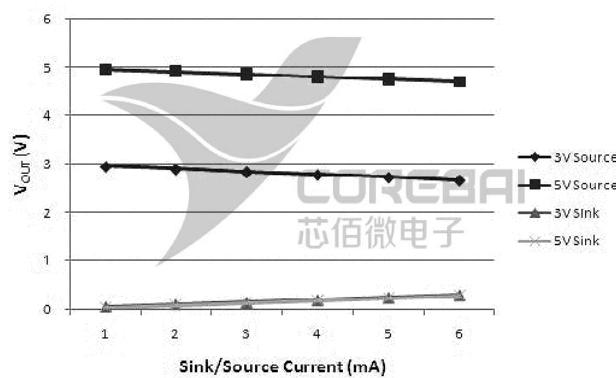

图 10. Vout Source and Sink Current Capability

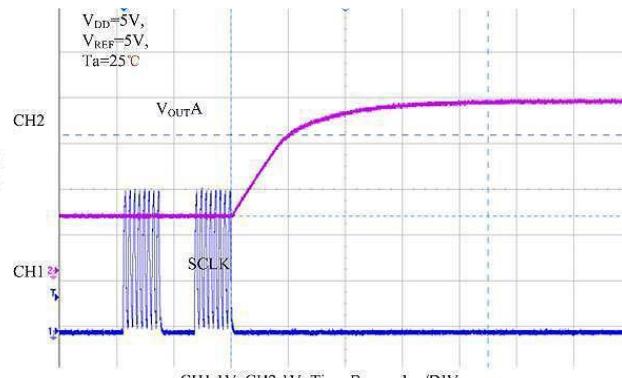

图 11. Half-scale setting

(0.25 to 0.75 Scale Code Change)

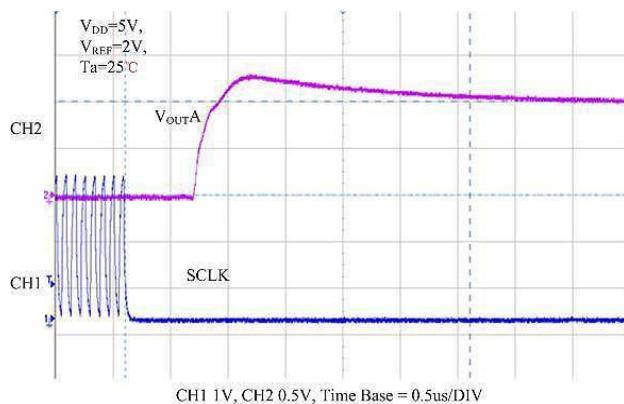

图 12. Exiting Power-down to Midscale

## 功能说明

CD53D04/CD53D14/CD53D24 是 4 路电阻串联分压式数模转换器 (DACs)，采用 CMOS 工艺制造，CD53D04/CD53D14/CD53D24 的分辨率分别为 8 位、10 位、12 位。每个产品都包含 4 个输出缓冲放大器，数据由 3 线串行接口写入。工作时由单电源供电，供电范围为 2.5V 到 5.5V，输出缓冲放大器提供轨至轨输出摆幅，压摆率为 0.7 V/us。四路数模转换器 (DACs) 共享独立的基准输入引脚。设备具有可编程休眠模式，在休眠模式下，所有的数模转换会在高阻抗输出模式下完全关闭。

一个数模转换通道架构包含一个串联分压式数模转换器，并且串联一个输出缓冲放大器。基准引脚的基准电压为数模转换器 (DAC) 提供基准电压。对数模转换器 (DAC) 的输入编码为标准二进制编码，合适的输出电压有下列公式给出：

$$V_{OUT} = \frac{V_{REF} \times D}{2^N} \quad \text{公式 1}$$

式中  $D$ =加载到 DAC 寄存器的二进制编码所对应的十进制值: CD53D04 (8 位), 0—255

CD53D14(10 位) , 0—1023

CD53D24(12 位) , 0—4095

$N$ =DAC 分辨率。

四路数模转换器 (DACs) 共享独立的基准输入引脚。基准输入电压没有缓冲。因为任何基准放大器的上裕量、下裕量所需要的电压没有限制，所以使用者会得到低至 0.25V 或者高至  $V_{DD}$  的基准电压。建议使用外部电路的缓冲基准电压。输入阻抗的典型值为 45k $\Omega$ 。

输出缓冲放大器在输出电路上能够产生轨至轨电压，当基准电压为  $V_{DD}$  时，输出电压范围为 0V 到  $V_{DD}$ 。放大器能够驱动对地 (GND) 或对  $V_{DD}$  2k $\Omega$  的负载，对地 (GND) 或对  $V_{DD}$  与电阻并联 500pF 电容，压摆率是 0.7V/us，半幅设定时间为 8us，误差  $\pm 0.5$ LSB (在 12 位元件上)。

CD54D04/CD53D14/CD53D24 具有电源重启功能，因此定义了电源启动状态。电源开机状态使用正常操作，输出电压设为 0V。输入和 DAC 寄存器设为 0，并且保持到有效写入序列加载到设备上。

CD54D04/CD53D14/CD53D24 由多用途、3 线串联接口控制，接口工作时钟速率达 30MHz，兼容 SPI, QSPI, MICROWIRE 和 DSP 接口标准。

## 3 线串联接口

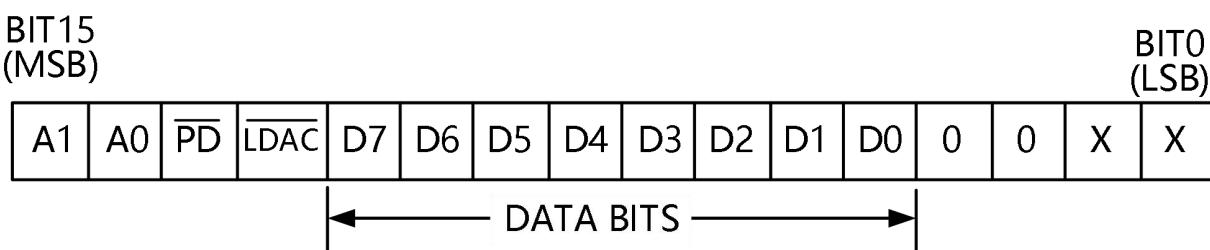

(a). CD53D04 输入移位寄存器内容

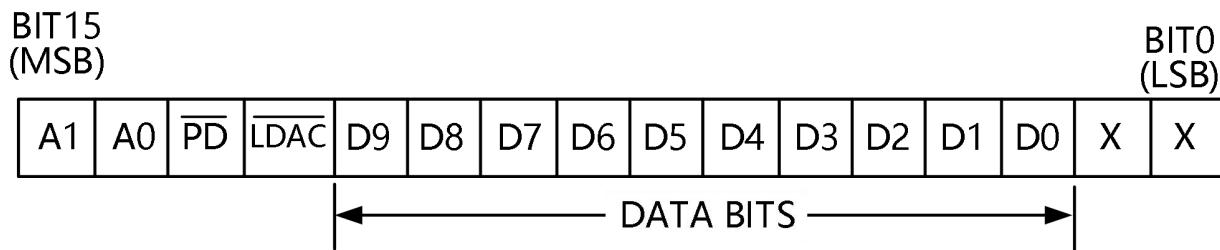

(b). CD53D14 输入移位寄存器内容

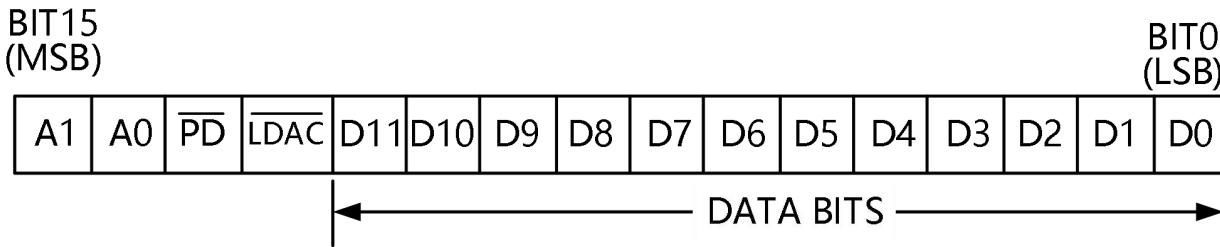

(c). CD53D24 Input Shift Register Contents

图 42. CD53D04/CD53D14/CD53D24 输入移位寄存器内容

## 输入移位寄存器

输入移位寄存器位宽为 16 位，在串联时钟输入控制下 ( $S_{clk}$ )，数据以 16 位形式加载到设备上。16 位字包含 4 个控制位，相邻为 10 或 12 位 DAC 数据，位数由设备类型决定。数据加载到最高有效位 (MSB，位 15)，前两位决定数据是否提供给 DAC A, DAC B, DAC C, 或者 DAC D，位 13 和位 12 控制 DAC 工作模式。位 13 是引脚下拉 (低电平有效)，决定设备是在正常模式还是休眠模式工作。位 12 表示异步 DAC 装载输入 (低电平有效)，当 DAC 寄存器和输出更新时控制输入。

表 6 (位地址)

| A1 | A0 | DAC 地址 |

|----|----|--------|

| 0  | 0  | DAC A  |

| 0  | 1  | DAC B  |

| 1  | 0  | DAC C  |

| 1  | 1  | DAC D  |

## 地址和控制位

PD: 0:所有四路数模转换器 (DACs) 进入休眠模式，只消耗 200nA @ 5V，数模转换器 (DAC) 输出进入高阻抗状态。

1: 正常工作模式。

LDAC 0: 所有 4 路数模转换器 (DAC) 寄存器和输出在写入序列完成的同时更新。

1: 只有地址输入寄存器更新，数模转换器 (DAC) 寄存器内容没有变化。

CD53D24 的 DAC 数据使用所有 12 位地址，CD53D14 使用 10 位地址，忽略 2 个低位有效位。

CD53D04 使用 8 位地址，忽略 4 位低位地址。数据格式为标准二进制，所有为 0 的地址位表示 0 伏输出，所有为 1 的地址位表示满量程输出( $V_{REF}-1$ LSB)。

同步输入是条件触发输入，这个输入用作帧同步信号和芯片使能控制。只有同步信号为低电平时，数

据才被传送到设备。为了启动串行数据传送，使用低电平。当同步信号变为低电平时，在 16 位时钟脉冲时钟下降沿，串行数据转换到设备输入转换寄存器。在第 16 个时钟下降沿之后，数据和时钟脉冲都被忽略，因为时钟信号和数据输入缓冲会进入休眠模式。没有更多的串行数据进行转换，直到同步信号再次进入高低电平，同步信号会在 16 个时钟脉冲的下降沿置为高电平。

串行数据转换结束后，数据由输入转换寄存器自动传送到所选的数模转换器（DAC）的输入寄存器。如果同步信号在第 16 个时钟下降沿之前置高电平，数据转换器中止工作，DAC 输入寄存器内容不会更新。

当数据已经传送到其中三路 DAC 输入寄存器中，所有 DAC 寄存器和所有的 DAC 输出同时通过 LDAC 低电平更新，并写入到剩余的 DAC 输入寄存器中。

### 低功耗串行接口

为进一步减少设备功耗，仅在同步信号下降沿，数据写入设备时，接口进入完全工作状态。一旦 16 位控制字写入设备，时钟信号和数据输入缓冲随后进入休眠模式。设备仅在下一次同步信号下降沿重新工作。

### 双缓冲接口

CD53D04/CD53D14/CD53D24 数模转换器（DACs）具有双缓冲接口，包含两组寄存器：输入寄存器和 DAC 寄存器。输入寄存器直接连接输入转换寄存器，数字编码在有效写入序列完成后传输到与之关联的输入寄存器中。DAC 寄存器包含分压电阻串使用的数字编码。

由 LDAC 位控制使用 DAC 寄存器。当 LDAC 位设为高电平时，DAC 寄存器进入闭止状态，因此输入寄存器能够改变状态而没有影响 DAC 寄存器的内容。然而，当 LDAC 位设为低电平时，所有的 DAC 寄存器在完成写入序列后更新内容。

如果使用者需要同时更新所有的 DAC 输出，这个控制是有用的。使用者能够分别写入三路输入寄存器，然后通过设置 LDAC 位为低电平，将数据写入剩下的 DAC 输入寄存器，之后所有的输入数据会同时更新。

这些设备还包括额外的功能，DAC 寄存器不会更新，除非输入寄存器在最近一次 LDAC 位设为低电平时已经更新。通常，当 LDAC 位设为低电平时，DAC 寄存器会存储输入寄存器的内容。CD53D04/CD53D14/CD53D24 只在最近一次 DAC 寄存器更新数据引起输入寄存器改变时，更新 DAC 寄存器数据，从而消除不必要的数字串扰。

### 休眠模式

CD53D04/CD53D14/CD53D24 具有低功耗特点，在 3V 供电电压下功耗仅为 1.5mW，在 5V 供电电压下功耗仅为 3mW。可以将位 13(PD)控制位设为 0 而使数模转换器（DACs）进入休眠模式，这样设备处于不使用的状态，以此可以进一步减少设备的功率消耗。

当控制位 (PD) 设为 1 时，所有的数模转换器（DACs）会正常工作，典型的供电电流为 5V 下 600uA (3V 下 500uA)。然后，在休眠模式下，所有的数模转换器（DACs）会进入休眠模式，供电电流会降至 5V 下 200nA (3V 下 80nA)。不仅供电电流降低，而且正在进行输出的放大器输出也会内部切换，使电路成为断路电路。这个特点的优点是当设备在休眠模式下输出具有三个状态，无论任何设备连接到 DAC 放大器的输入，都会有一个明确的输入条件。

偏压发生器、输出放大器、电阻串和其他所有相关的线性电路都会在设备休眠模式下关闭。然而，寄存器存储的内容不会因为器件关闭受到影响。退出休眠模式时间的典型值为 5us，这个时间是从第 16 个时钟脉冲的下降沿到输出电压偏离休眠模式时电压。

## 典型应用电路

CD53D04/CD53D14/CD53D24 可作为大幅度基准电压使用，在 0V 到  $V_{DD}$  基准电压范围内，设备提供具有完整功能的单象限乘法器的能力。更加典型的情况是，这些设备可作为固定、精确基准电压使用。

如果需要 0V 到  $V_{DD}$  输出电压范围，最简单的解决办法是将基准输入连接到  $V_{DD}$  上。当供电电压不太稳定且有噪声，CD53D04/CD53D14/CD53D24 能够由基准电压供电。例如，使用 5V 基准电压时，需要 600  $\mu$ A 的供电电流，大概 112 $\mu$ A 电流流向基准电压输入，在 DAC 输出上没有负载。当 DAC 输出连接负载时，基准电压产生供电电流提供给负载。

## CD53D04/CD53D14/CD53D24 多路解码

CD53D04/CD53D14/CD53D24 的同步引脚在应用中解码数模转换器 (DACs) 的数字。在这个应用中，系统中所有数模转换器 (DACs) 接收到相同的串行时钟和串行数据，但是同步操作只能是在任一时间激活其中一个设备，允许系统中的一个数模转换器工作。74HC139 可以用来当作 2 至 4 线解码器 处理系统中的任一数模转换器 (DACs)。为避免时序错误，当编码地址输入处于转换状态时，使能输入必须处于非活动状态。

## 电源旁路和接地

准确性在任何电路中都很重要，仔细考虑供电电源和接地回路布线能确保额定性能发挥。布置有 CD53D04 / CD53D14 / CD53D24 的印刷电路板设计时，逻辑段和数字段是分开的，并且局限在电路板特定区域内。如果 CD53D04 / CD53D14/ CD53D24 在系统中，该系统中多个设备需要模拟地 (AGND) 到数字地 (DGND) 的连接，该连接仅需一个连接点。星形接地连接点应建立在里设备尽可能近的地方。

CD53D04/CD53D14/CD53D24 有一个电容量充足的 10 $\mu$ F 电源旁路电容，在供电电源上并联一个 0.1 $\mu$ F 电容，这个电容布置在离芯片封装结构尽可能近的位置，正好与设备相接。10  $\mu$ F 电容类型是钽珠电容，0.1 $\mu$ F 电容包含低电平有效串联电阻 (ESR) 和有效串联电感 (ESI)。

CD53D04/CD53D14/CD53D24 的电源线使用尽量加宽的电源线，可以提供低阻抗，降低电源线故障影响。将快速切换的信号，如时钟信号，通过数字接地进行屏蔽，避免将噪声辐射到电路板其他部分，也从不以接近基准输入电压的方式运行，避免数字和逻辑信号的交叉。板子正反两面的布线应该成直角，这样会减少信号通过电路板时的馈通影响。

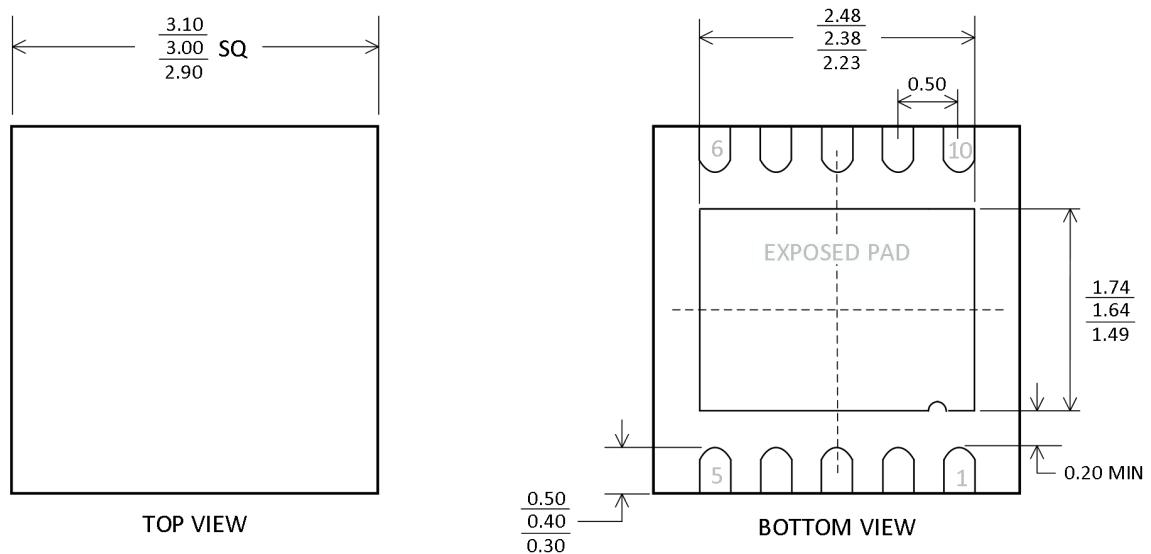

## 封装外形及尺寸

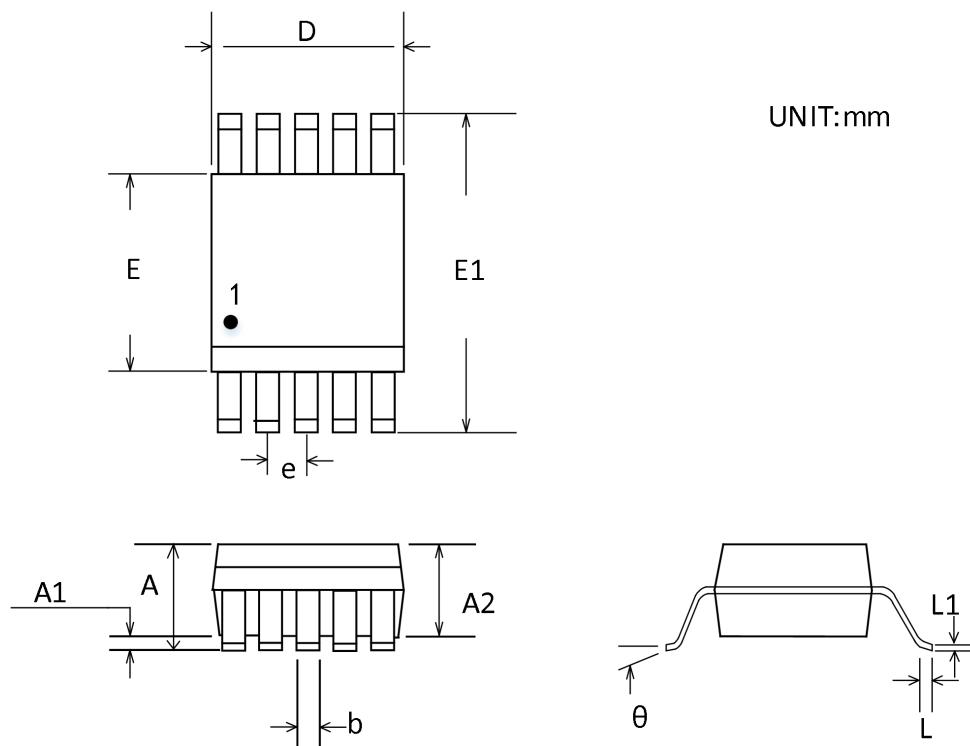

### MSOP-10

| 符号 | 尺寸       |      |      |

|----|----------|------|------|

|    | 最小值      | 正常值  | 最大值  |

| A  | --       | --   | 1.10 |

| A1 | 0.05     | --   | 0.15 |

| A2 | 0.75     | 0.85 | 0.95 |

| b  | 0.15     | --   | 0.30 |

| D  | 2.90     | 3.00 | 3.10 |

| E  | 2.90     | 3.00 | 3.10 |

| E1 | 4.65     | 4.90 | 5.15 |

| e  | 0.50 BSC |      |      |

| L  | 0.40     | 0.55 | 0.70 |

| L1 | 0.13     | --   | 0.23 |

| θ  | 0        | --   | 6°   |

**QFN-10**

## 包装/订购信息

| 产品型号       | 温度范围        | 产品封装    | 运输及包装数量       |

|------------|-------------|---------|---------------|

| CD53D04AMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D04BMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D04AQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

| CD53D04BQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

| CD53D14AMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D14BMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D14AQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

| CD53D14BQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

| CD53D24AMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D24BMS | -40°C~105°C | MSOP-10 | 编带和卷盘,每卷 3000 |

| CD53D24AQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

| CD53D24BQF | -40°C~105°C | QFN-10  | 编带和卷盘,每卷 5000 |

## 修订日志

| 版本   | 修订日期     | 变更内容 | 变更原因 | 制作 | 审核  | 备注 |

|------|----------|------|------|----|-----|----|

| V1.0 | 2025.7.1 | 初版生成 | 常规更新 | WW | LYL |    |