# CD94AD34

12 位、370 MSPS/500 MSPS、1.8 V 模数转换器

版本：Rev 1.0.0 日期：2026-1-4

## 产品特性

- 分辨率: 12bit

- 采样率: 500MSPS;

- SFDR > 65dB;

- 可变输入范围 1.18Vp-p 到 1.6Vp-p

- PIN 兼容 AD9434 系列

## 产品应用

- 无线、宽带通信

- 接收器

- 通信测试设备

- 雷达和卫星子系统

- 功率放大器的线性化

- 无线、宽带通信

## 产品描述

CD94AD34 是一款 12 位、单片采样模数转换器 (ADC)，专门为高性能、低功耗以及易于使用进行了优化设计。它的转换速率能达到 500 MSPS，在宽带应用中有很好的动态性能表现。所有需要的功能都集成在片内，其中包括了采样保持放大器(SHA)和片内基准电压源，以提供完整的信号转换解决方案。

VREF 引脚可用于改变内部基准电压或接受来自外部的参考电压（外部基准模式需通过 SPI 端口开启）。

此款 ADC 需要 1.8 V 的模拟电源供电，以及一个差分时钟来保持出色的 ADC 整体性能。数字输出是兼容 LVDS (ANSI-644) 的，数据格式为二进制补码、格雷码或偏移二进制。有数据输出时钟来确保相应数据输出具有正确的时序。

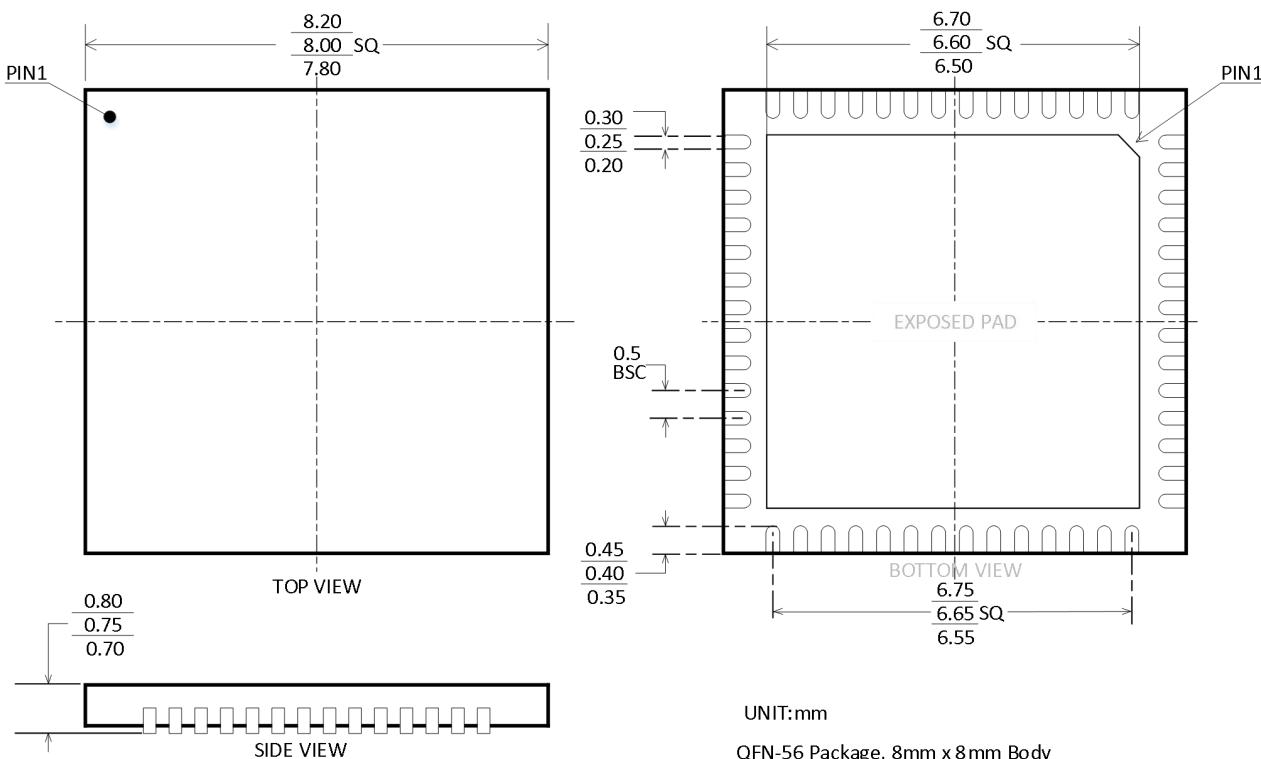

该产品采用 SiGe BiCMOS 工艺制造，56 引线塑料封装 (QFN56)，可有效替代美国 ADI 公司的 AD9434BCPZ-500。

## 目录

|           |        |

|-----------|--------|

| 产品特性      | - 1 -  |

| 产品应用      | - 1 -  |

| 产品描述      | - 1 -  |

| 功能框图      | - 3 -  |

| 引脚配置      | - 4 -  |

| 引脚简述      | - 4 -  |

| 推荐工作条件    | - 6 -  |

| 推绝对最大额定值  | - 6 -  |

| 性能参数      | - 6 -  |

| 典型应用线路图   | - 10 - |

| 注意事项      | - 15 - |

| 常见故障及处理方法 | - 15 - |

| 产品外形图     | - 16 - |

| 包装/订购信息   | - 16 - |

| 修订日志      | - 17 - |

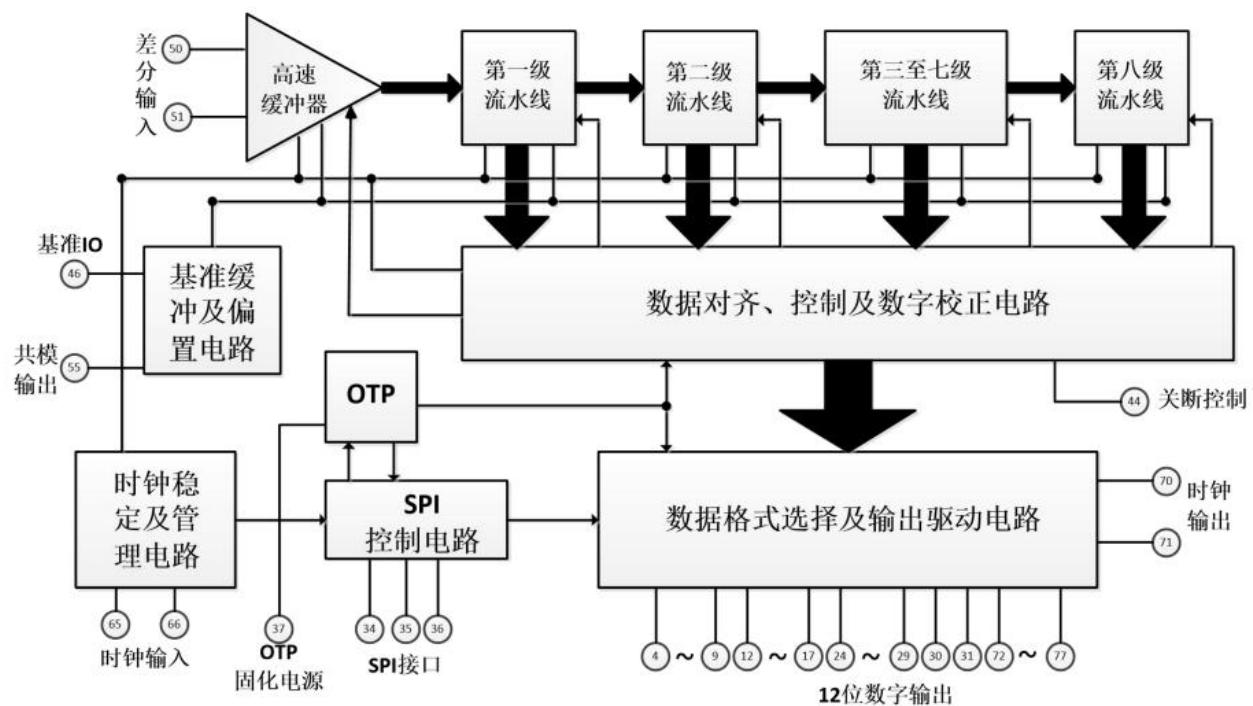

## 功能框图

18 位 5MSPS A/D 转换器功能框图如图 1。

图 1. 功能框图

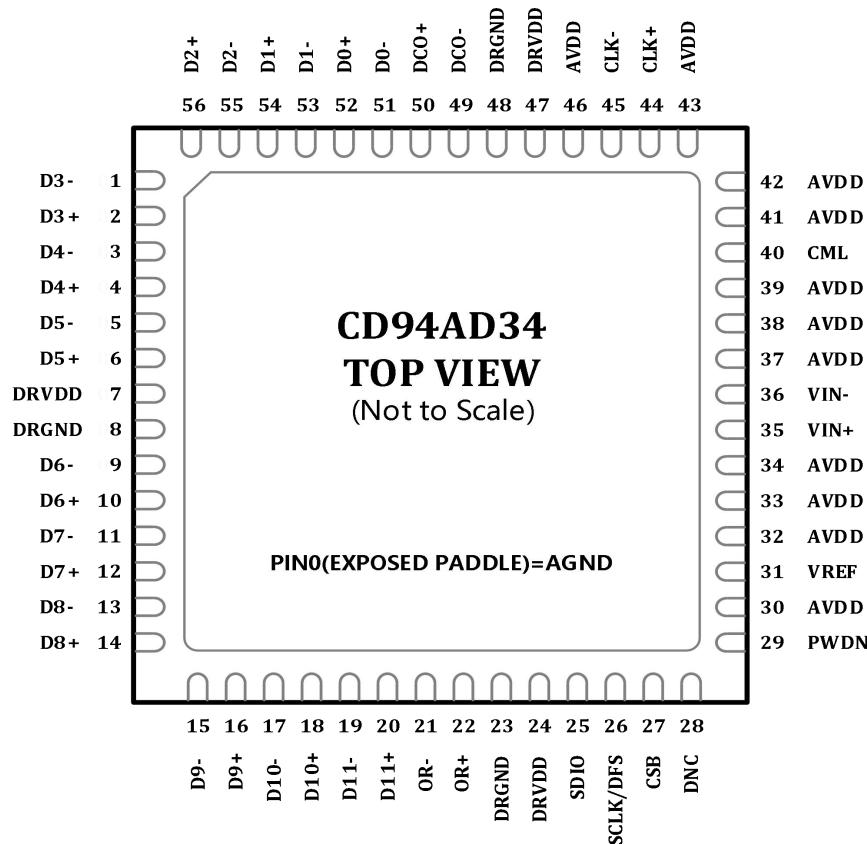

## 引脚配置

18 位 A/D 转换器引出端如图 4。

图 2.引脚配置图

## 引脚简述

| 引脚序号    | 符号    | 功能                |

|---------|-------|-------------------|

| 0       | AGND  | 模拟地。外露焊盘必须焊接到接地层。 |

| 1       | D3-   | D3 差分输出, 负端       |

| 2       | D3+   | D3 差分输出, 正端       |

| 3       | D4-   | D4 差分输出, 负端       |

| 4       | D4+   | D4 差分输出, 正端       |

| 5       | D5-   | D5 差分输出, 负端       |

| 6       | D5+   | D5 差分输出, 正端       |

| 7,24,47 | DRVDD | 1.8V 数字电源         |

| 8,23,48 | DRGND | 数字地               |

| 9       | D6-   | D6 差分输出, 负端       |

| 10      | D9+   |                   |

| 11      | D10-  |                   |

| 12      | D10+  |                   |

| 13      | D11-  |                   |

| 14      | D11+  |                   |

| 15      | OR-   |                   |

| 16      | OR+   |                   |

| 17      | DRGND |                   |

| 18      | DRVDD |                   |

| 19      | SDIO  |                   |

| 20      | CML   |                   |

| 21      | CSB   |                   |

| 22      | DNC   |                   |

| 23      | VREF  |                   |

| 24      | AVDD  |                   |

| 25      | AVDD  |                   |

| 26      | AVDD  |                   |

| 27      | AVDD  |                   |

| 28      | PWDN  |                   |

| 30      | AVDD  |                   |

| 31      | AVDD  |                   |

| 32      | AVDD  |                   |

| 33      | AVDD  |                   |

| 34      | AVDD  |                   |

| 35      | VIN+  |                   |

| 36      | VIN-  |                   |

| 37      | AVDD  |                   |

| 38      | AVDD  |                   |

| 39      | AVDD  |                   |

| 40      | CML   |                   |

| 41      | AVDD  |                   |

| 42      | AVDD  |                   |

|                                           |          |                                  |

|-------------------------------------------|----------|----------------------------------|

| 10                                        | D6+      | D6 差分输出, 正端                      |

| 11                                        | D7-      | D7 差分输出, 负端                      |

| 12                                        | D7+      | D7 差分输出, 正端                      |

| 13                                        | D8-      | D8 差分输出, 负端                      |

| 14                                        | D8+      | D8 差分输出, 正端                      |

| 15                                        | D9-      | D9 差分输出, 负端                      |

| 16                                        | D9+      | D9 差分输出, 正端                      |

| 17                                        | D10-     | D10 差分输出, 负端                     |

| 18                                        | D10+     | D10 差分输出, 正端                     |

| 19                                        | D11-     | D11 差分输出, 负端                     |

| 20                                        | D11+     | D11 差分输出, 正端                     |

| 21                                        | OR-      | 溢出判断位, 负端                        |

| 22                                        | OR+      | 溢出判断位, 正端                        |

| 25                                        | SDIO     | SPI 数据输入/输出 (串行模式)               |

| 26                                        | SCLK/DFS | SPI 时钟 (串行模式) /输出数据格式选择 (外部引脚模式) |

| 27                                        | CSB      | SPI 片选 (低电平有效)                   |

| 28                                        | DNC      | 空                                |

| 29                                        | PWDN     | 关断模式选择                           |

| 30,32 to<br>34,37 to<br>39,41 to<br>43,46 | AVDD     | 1.8V 模拟电源                        |

| 35                                        | VIN+     | 模拟差分输入正端                         |

| 36                                        | VIN-     | 模拟差分输入负端                         |

| 40                                        | CML      | 共模电压偏置输出                         |

| 44                                        | CLK+     | 时钟差分输入, 正端                       |

| 45                                        | CLK-     | 时钟差分输入, 负端                       |

| 49                                        | DCO-     | 数据时钟, 负端                         |

| 50                                        | DCO+     | 数据时钟, 正端                         |

| 51                                        | D0-      | D0 差分输出, 负端                      |

| 52                                        | D0+      | D0 差分输出, 正端                      |

| 53                                        | D1-      | D1 差分输出, 负端                      |

| 54                                        | D1+      | D1 差分输出, 正端                      |

| 55                                        | D2-      | D2 差分输出, 负端                      |

|                               |     |             |

|-------------------------------|-----|-------------|

| 56                            | D2+ | D2 差分输出, 正端 |

| 注 1: 封装底部的热沉焊盘为模拟地端 $GND_A$ 。 |     |             |

| 注 2: NC 端, 正常使用时悬空。           |     |             |

## 推荐工作条件

- 工作频率 ( $f_{CLK}$ ) :  $\leq 500MHz$

- 模拟电源电压 ( $V_{CC}$ ) :  $1.75V \sim 1.9V$

- 数字电源电压 ( $V_{DD}$ ) :  $1.75V \sim 1.9V$

- 模拟输入共模电压 ( $V_{IC}$ ) :  $1.6V \sim 1.8V$

- 工作环境温度 ( $T_A$ ) :  $-40^{\circ}C \sim 85^{\circ}C$

- 输入信号幅度范围 (峰峰值) ( $V_{IN(P-P)}$ ) :  $\leq 1.5V$

## 推绝对最大额定值

- 模拟电源电压 ( $V_{CC}$ ) :  $2V$

- 数字电源电压 ( $V_{DD}$ ) :  $2V$

- 贮存温度 ( $T_{stg}$ ) :  $-65^{\circ}C \sim 150^{\circ}C$

- 结温 ( $T_J$ ) :  $175^{\circ}C$

- 引线耐焊接温度 ( $Th$ ) (10s) :  $300^{\circ}C$

## 性能参数

| 参数                |           | 测试条件 | 最小值  | 典型值 | 最大值  | 单位   |

|-------------------|-----------|------|------|-----|------|------|

| 分辨率               | RES       | --   | 12   |     |      | bits |

| 失调误差              | $E_O$     | --   | -5.0 | --  | 5.0  | mV   |

| 增益误差              | $E_G$     | --   | -9   | --  | 9    | %FS  |

| 微分线性误差            | $E_{DL}$  | --   | -1.5 | --  | 1.5  | LSB  |

| 积分线性误差            | $E_L$     | --   | -4.5 | --  | 4.5  | LSB  |

| 内部参考电压            | $V_{REF}$ | --   | 0.7  | --  | 0.8  | LSB  |

| 电源电流 <sup>a</sup> | I         | --   | --   | --  | 500  | mA   |

| LVDS差分输出电压        | $V_{od}$  | --   | 200  | --  | 500  | mV   |

| LVDS 共模输出电压       | $V_{os}$  | --   | 1.0  | --  | 1.45 | V    |

| 功耗                | $P_D$     | --   | --   | --  | 900  | mW   |

|         |           |                                                                   |      |    |    |      |

|---------|-----------|-------------------------------------------------------------------|------|----|----|------|

| 待机功耗    | $P_{SDB}$ | --                                                                | --   | -- | 60 | mW   |

| 休眠功耗    | $P_{PDN}$ | --                                                                | --   | -- | 12 | mW   |

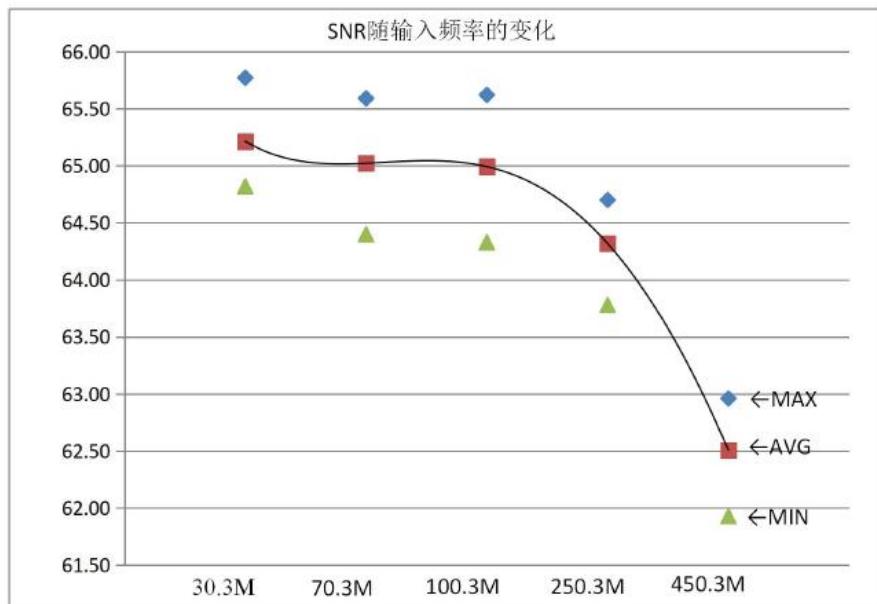

| 信噪比     | SNR       | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=30.3MHz$                  | 63   | -- | -- | dBFS |

|         |           | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=450.3MHz$                 | 61   | -- | -- |      |

|         |           | $f_{CLK}=500MHz, T_A=-40^\circ C \sim 85^\circ C, f_{IN}=30.3MHz$ | 58   | -- | -- |      |

| 信噪失真比   | SINAD     | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=30.3MHz$                  | 62   | -- | -- | dBFS |

|         |           | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=450.3MHz$                 | 60   | -- | -- |      |

|         |           | $f_{CLK}=500MHz, T_A=-40^\circ C \sim 85^\circ C, f_{IN}=30.3MHz$ | 57   | -- | -- |      |

| 有效位     | ENOB      | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=30.3MHz$                  | 10.0 | -- | -- | bits |

|         |           | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=450.3MHz$                 | 9.5  | -- | -- |      |

|         |           | $f_{CLK}=500MHz, T_A=-40^\circ C \sim 85^\circ C, f_{IN}=30.3MHz$ | 9.2  | -- | -- |      |

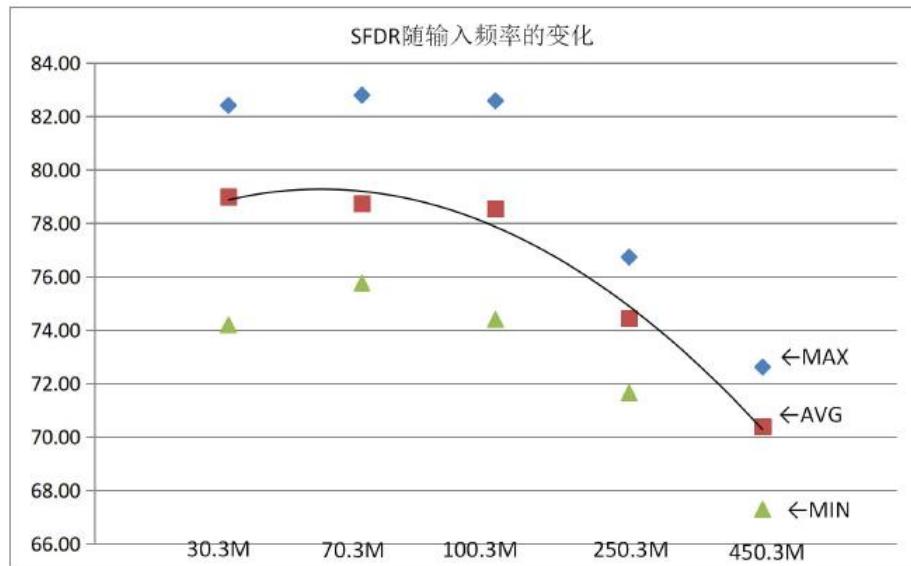

| 无杂散动态范围 | SFDR      | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=30.3MHz$                  | 72   | -- | -- | dBFS |

|         |           | $f_{CLK}=500MHz, T_A=25^\circ C, f_{IN}=450.3MHz$                 | 66   | -- | -- |      |

|         |           | $f_{CLK}=500MHz, T_A=-40^\circ C \sim 85^\circ C, f_{IN}=30.3MHz$ | 65   | -- | -- |      |

| 数据延迟时间  | $t_{PD}$  |                                                                   | --   | -- | 10 | ns   |

Note:<sup>a</sup> 电源电流为模拟电源电流 ( $I_{CC}$ ) 和数字电源电流 ( $I_{DD}$ ) 的总和。

## 典型特性曲线图

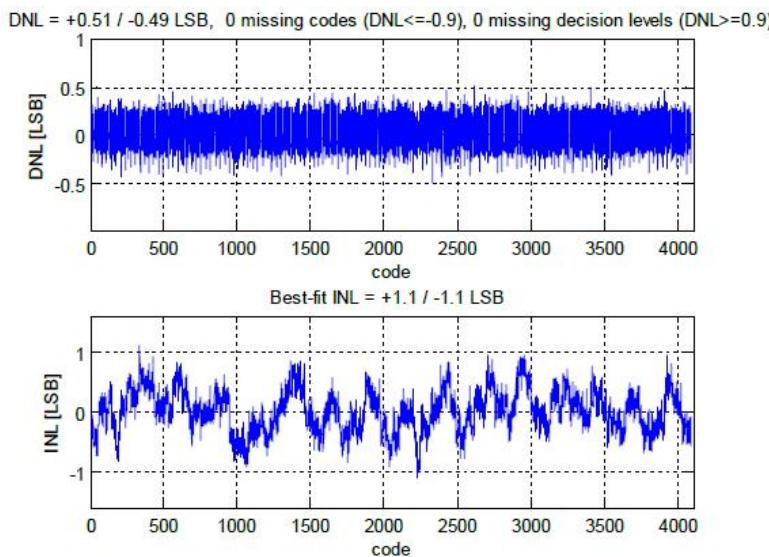

### 1、DNL、INL 测试结果

测试条件：

采样率：fCLK=500MHz；输入信号频率 fIN=30.3MHz；测试结果：DNL： -0.51/+0.49 LSB

INL： -1.1/+1.1 LSB

图 3. DNL、INL 测试结果

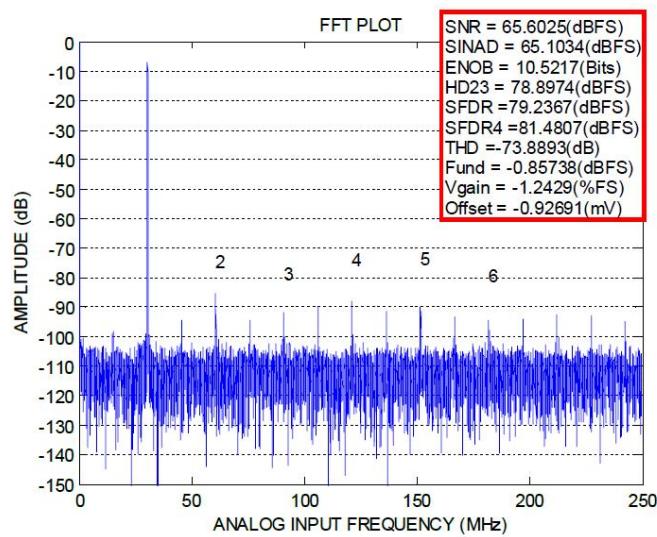

### 2、动态参数测试结果

测试条件：

采样率：fCLK=499.99970304MHz；

输入信号频率 fIN=30.28867830MHz；

测试结果：

SFDR=79.23dBFS；

HD2, 3nd = 78.89dBFS；

HD4nd = 81.48dBFS；

SNR = 65.6dBFS；

图 4. 动态指标测试结果

## 3、SNR、SFDR 随采样频率变化曲线

图 5. SNR 随采样频率变化曲线

图 6. SFDR 随采样频率变化曲线

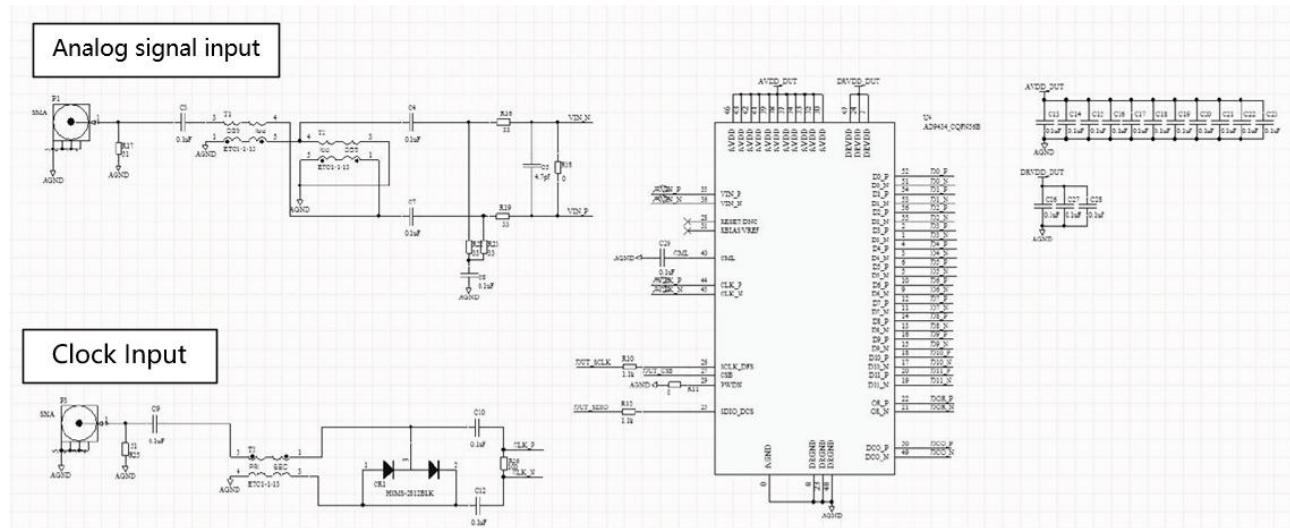

## 典型应用线路图

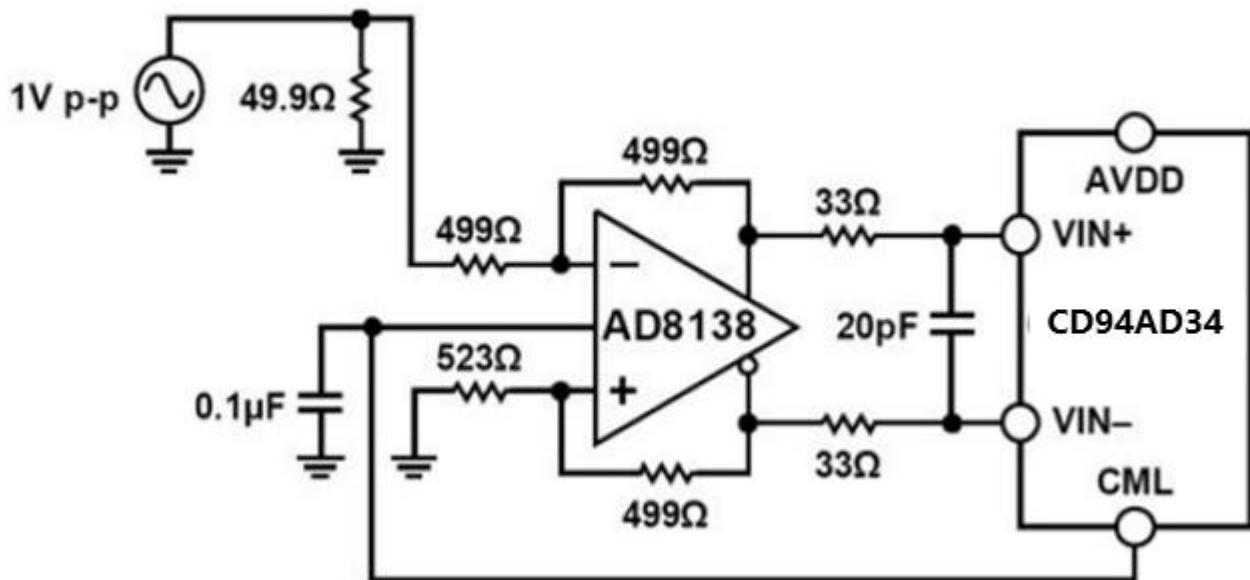

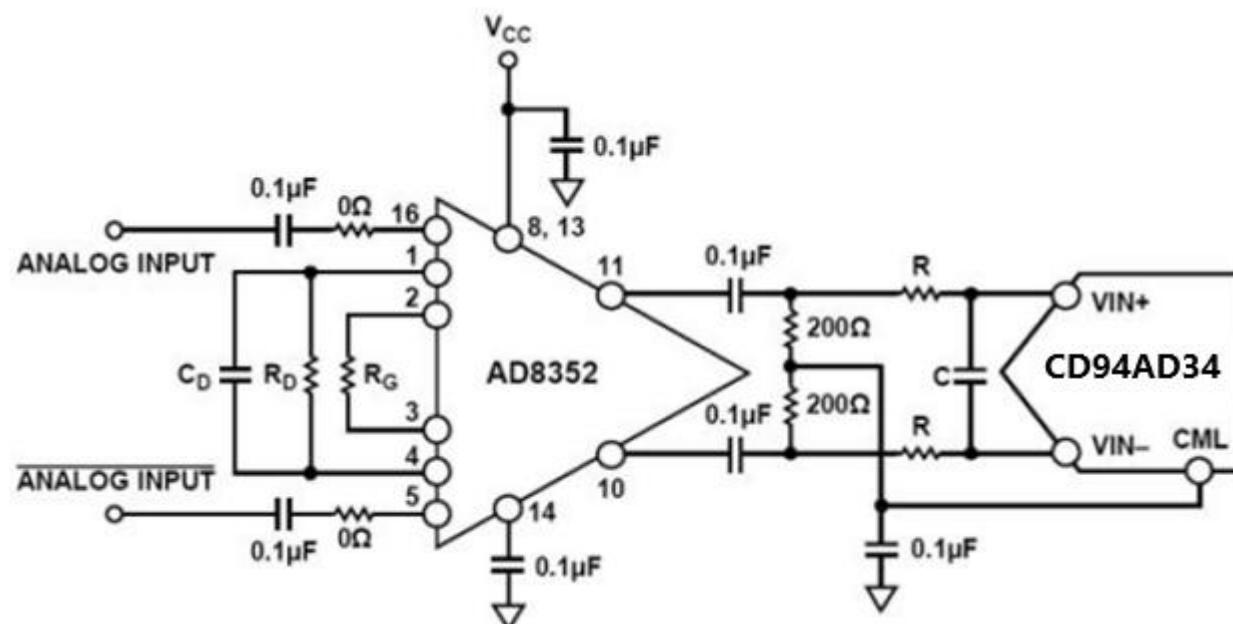

### 模拟输入电路

通过差分输入配置驱动 CD94AD34 时，可实现芯片的最佳性能。在基带应用中，AD8138 差分驱动器能够为 ADC 提供出色的性能和灵活的接口。AD8138 输出共模电压很容易设置到 AVDD/2+0.5 V，且此驱动器可以配置为 Sallen-Key 滤波器拓扑电路结构，从而对输入信号进行带宽限制。

图 7. 利用 AD8138 进行差分输入配置

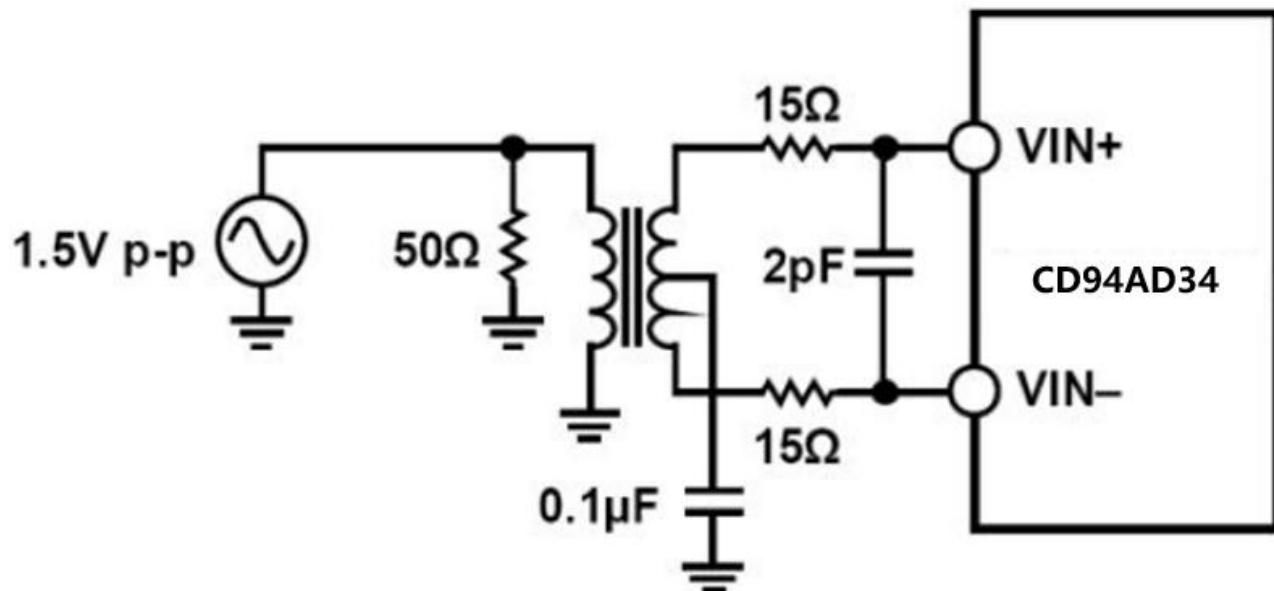

当输入频率处于第二或更高奈奎斯特区域时，大多数放大器的噪声性能无法满足要求以达到 CD94AD34 真正的 SNR 性能。对于频率在 70 MHz 到 100 MHz 的中频欠采样应用中这个现象尤为

明显。对于这类应用，建议使用的输入配置是差分双巴伦耦合。在选择变压器时，必需考虑其信号特性。大多数射频变压器在工作频率低于几兆赫兹时产生饱和现象；信号功率过大也可导致内核磁芯饱和，从而引起失真。

在任何配置中，并联电容值  $C$  均取决于输入频率和源阻抗，并且可能需要降低电容量或去掉该并联电容。

图 8. 差分变压器耦合配置

频率在第二奈奎斯特区域内的时候，除了使用变压器耦合输入外，还可以使用 AD8352 差分驱动器，实例如图 9 所示。

图 9. 利用 AD8352 进行差分输入配置

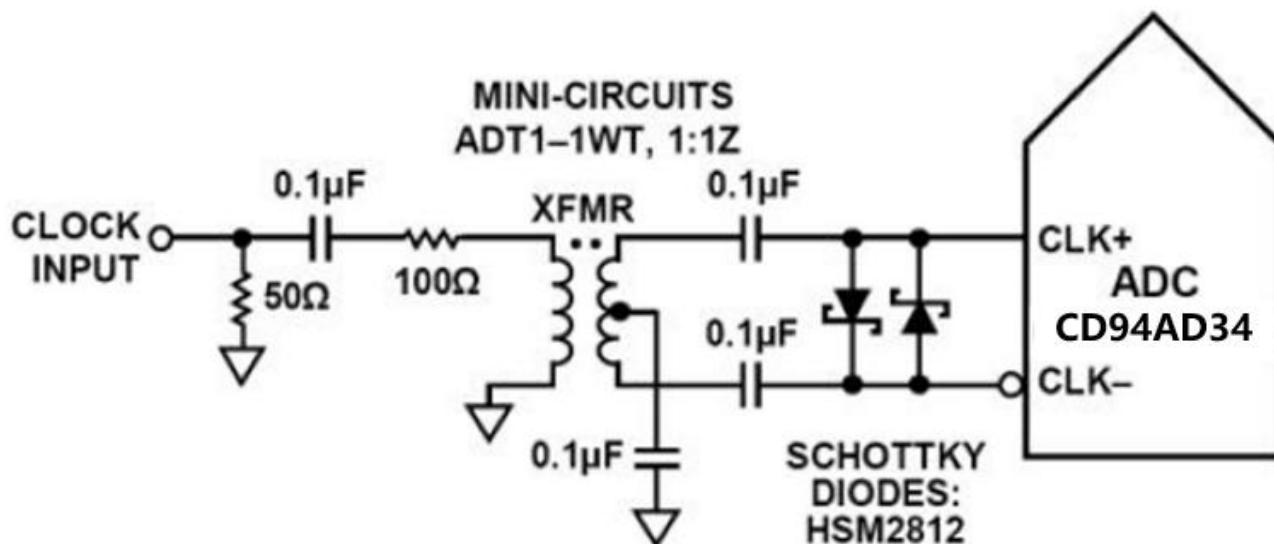

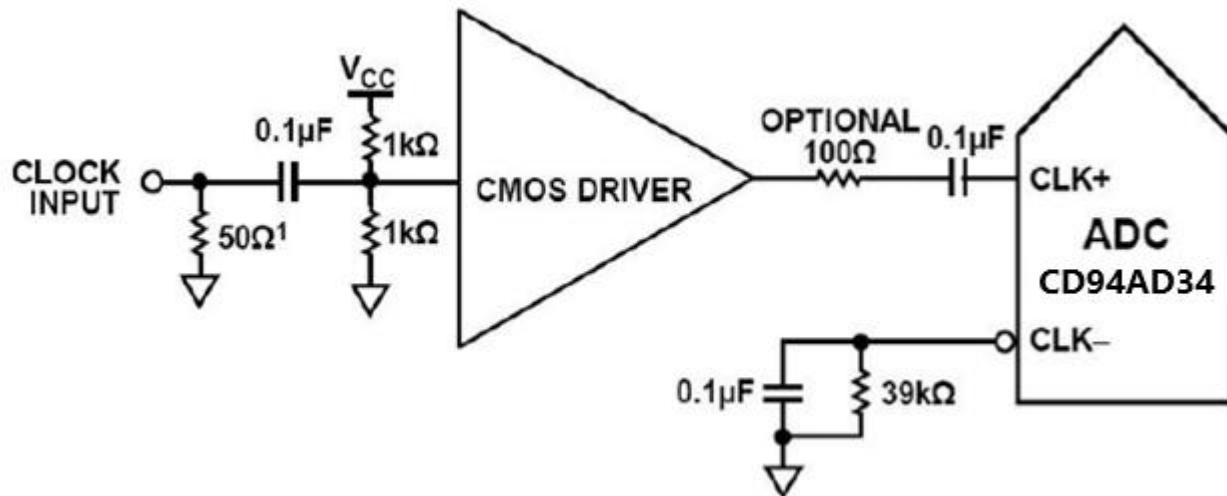

## 时钟输入电路

为了充分发挥芯片的性能, 应利用一个差分信号作为 CD94AD34 采样时钟输入端(CLK+ 和 CLK-)

的时钟信号。通常，应使用一个变压器或两个电容器将该信号交流耦合到 CLK+引脚和 CLK-引脚。CLK+和 CLK-引脚有约 0.9 V 的内部偏置，无需外部偏置。若时钟信号是直流耦合的，那么就要使共模电压保持在 0.9 V 的范围内。

图 10 显示了一种为 CD94AD34 提供时钟信号的首选方法。利用射频变压器，可将低抖动时钟源的单端信号转换成差分信号。跨接在变压器次级上的背对背肖特基二极管可以将输入到 CD94AD34 中的时钟信号限制为约差分 0.8 V 峰峰值。这样，既可以保留信号的快速上升和下降时间，还可以防止时钟的大电压摆幅馈通至 CD94AD34 的其它部分，这一点对低抖动性能来说非常重要。

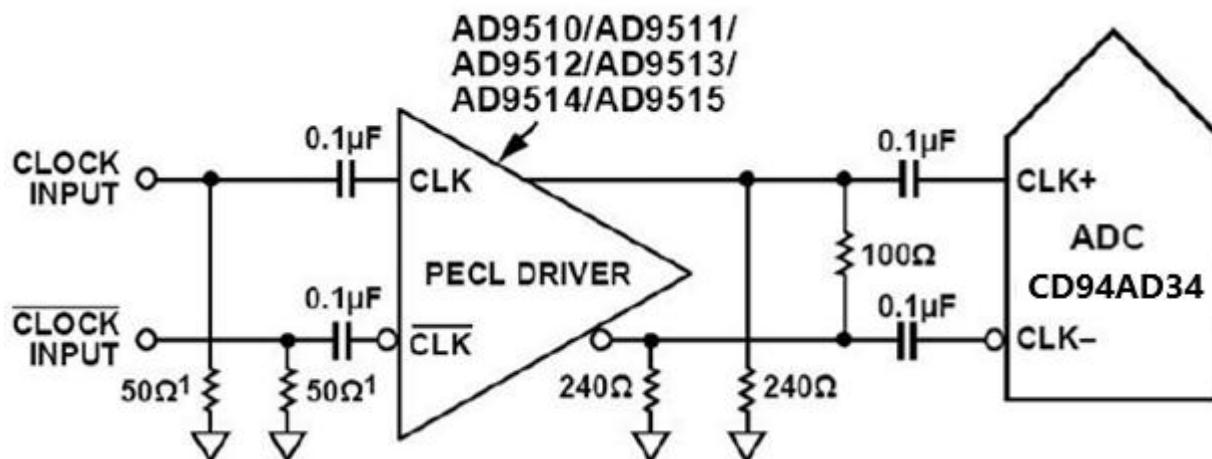

如果没有低抖动的时钟源，那么，另一种方法是对差分 PECL 信号进行交流耦合，并传输至采样时钟输入引脚(如图 11 所示)。AD9510/AD9511/AD9512/AD9513/AD9514/AD9515 系列时钟驱动器具有出色的抖动性能。

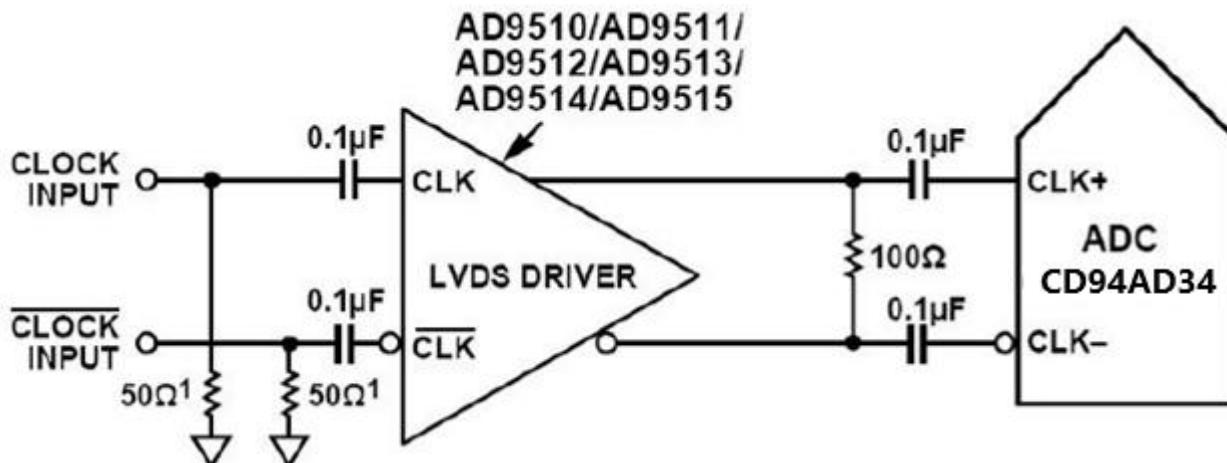

图 12. 差分 LVDS 采样时钟

在某些应用中，可以利用单端 CMOS 信号来驱动采样时钟输入。在此类应用中，CLK+引脚直接由 CMOS 门电路驱动，CLK-引脚则通过一个 0.1 F 电容旁路至地。用 1.8 V CMOS 信号驱动 CLK+时，要求通过一个 0.1 F 电容与一个 39 k 电阻的并联偏置 CLK-引脚(见图 13)。

图 13. 单端 1.8 V CMOS 输入时钟

## 数字输出

默认状态下，CD94AD34 的差分输出数据格式符合 ANSI-644 LVDS 标准。数据格式可以通过 SPI 改成低功耗、较少信号选择、类似于 IEEE 1596.3 标准的格式。此 LVDS 标准能进一步减少芯片的功耗，约 39mW。想要了解更多相关信息请参阅国外 AD9434BCPZRL7-500 存储器地址功能部分。LVDS 驱动器的电流来自于片内，每个输出位的输出电流大小一般被设置为 3.5 mA。在 LVDS 接收机的输入端加上 100 Ω 的终端电阻将产生 350 mV 的摆幅。CD94AD34 的 LVDS 型输出数据格式有利于与定制的 ASIC 和 FPGA 中的 LVDS 接收器相连接，在噪声高的环境中能有很好的开关性能。建议将带有 100 Ω 的终端电阻的单一点对点网络拓扑结构放置在离接收器越近的地方越好。接收器的终端放置的过远或者糟糕的差分布线将导致时序错误。建议走线长度不要超过 24 英寸，且差分输出走线要放在一起且长度相同。

## 输出码和模拟输入的关系表

| 输入                     | 条件                | 偏移二进制模式,<br>D11 to D0 | 二进制补码模式<br>mode, D11 到 D0 | OR± |

|------------------------|-------------------|-----------------------|---------------------------|-----|

|                        |                   | D11 to D0             | mode, D11 to D0           |     |

| $V_{IN+}$ to $V_{IN-}$ | $< -0.75-0.5$ LSB | 0000 0000 0000        | 1000 0000 0000            | 1   |

| $V_{IN+}$ to $V_{IN-}$ | $= -0.75$         | 0000 0000 0000        | 1000 0000 0000            | 0   |

| $V_{IN+}$ to $V_{IN-}$ | $= 0$             | 1000 0000 0000        | 0000 0000 0000            | 0   |

| $V_{IN+}$ to $V_{IN-}$ | $= 0.75$          | 1111 1111 1111        | 0111 1111 1111            | 0   |

| $V_{IN+}$ to $V_{IN-}$ | $> 0.75+0.5$ LSB  | 1111 1111 1111        | 0111 1111 1111            | 1   |

### 数据输出格式

输出数据的格式默认为偏移二进制。

本电路的典型应用线路如下图所示，详细的内容可以参见国外 AD9434BCPZ-500 的产品手册。

图 14. 典型应用线路

## 注意事项

### 产品安装注意事项：

1. 要求应用对象电路板有一个完整干净的地。

2. 要求应用对象为多层布线板且内含独立的地层。

3. 要求应用对象电路板的数字地和模拟地尽量分离，不要将数字线布于模拟线旁边或于 ADC 底下。

4. AVDD, DRVDD 和 VCM 要接高质量的陶瓷旁路电容，且旁路电容要尽量靠近管脚，连接管脚和旁路电容的连线越短越宽越好。

### 产品使用注意事项：

1. 差分输入应尽量靠近且相互平行。

2. 输入连线应尽量短以最小化寄生电容和噪声引入。

3. 为了更好的散热并获得更好的电性能，芯片的底板应焊接到 PCB 板的一个大的地端，从而最大限度发挥封装的热性能。

4. 很重要的是，芯片的地应该通过尽量多的渠道和足够多的面积与 PCB 板的地层相连。

### 产品防护注意事项：

1. 静电电荷很容易在人体和测试设备上累积，并可能在没有察觉的情况下放电。尽管本产品具有专用 ESD 保护电路，但在遇到高能量静电放电时，可能会发生永久性器件损坏。因此，建议采取适当的 ESD 防范措施，以避免器件性能下降或功能丧失。

2. 超出绝对最大额定值可能会导致器件永久性损坏。这只是额定最值，不表示在这些条件下或者在任何其它超出本产品手册中所示的条件下，器件能够正常工作。长期在绝对最大额定值条件下工作会影响器件的可靠性。

## 常见故障及处理方法

1. 无信号输出：检查电源电压、输入信号、时钟是否正确加载。

2. 出现溢出信号：检查基准是否正常工作，输入信号幅度是否正确。

3. 器件工作不稳定：检查电源，保证电源电压稳定。

## 产品外形图

## QFN-56

图 15. 外形图

## 包装/订购信息

| 产品型号         | 温度范围       | 产品封装   | 运输及包装数量   |

|--------------|------------|--------|-----------|

| CD94AD34-500 | -40°C-85°C | QFN-56 | Tray, 260 |

| CD94AD34-370 | -40°C-85°C | QFN-56 | Tray, 260 |

## 修订日志

| 版本   | 修订日期      | 变更内容                   | 变更原因 | 制作 | 审核  | 备注 |

|------|-----------|------------------------|------|----|-----|----|

| V1.0 | 2025.5.20 | 初版生成                   | 常规更新 | WW | LYL |    |

| V1.0 | 2025.9.10 | 更新 QFN-56 POD          | 升级更新 | WW | LYL |    |

| V1.0 | 2026.1.4  | 更新引脚图 pin38,pin40 错误定义 | 错误更新 | WW | LYL |    |

|      |           |                        |      |    |     |    |